|

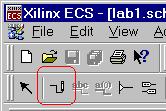

All wires that you want to provide input to or observe

output from must be connected to I/O pads. To do

this, you must first select the I/O pad tool (selected

in the window to the left) from the toolbar. Next,

observe the dialog box on the left side.

These pads determine the inputs and outputs for your

design. Moreover, they must be connected to wires on

your schematic (they cannot be connected directly to

the gate input.)

Adding in input pad is a simple matter of

selecting "Add an input marker" in the dialog on the

left side and clicking on the end of the wire whose

input you wish to define. From there, you must rename

the input pad to correspond to the constraints on your

design.

To rename an I/O pad, you can use one of two methods.

The first method is to double click the pad, and then

set the net name within the dialog box that appears.

The second is to simply right-click on the pad and

select Rename from the contextual menu that is

brought up. In either case, these names must match with

the settings used in the Constraints file, which

is detailed later in the lab.

The additon of an output pad is analogous to that

of the input. Select "Add an output marker" and place

it on the schematic. Once again, you must rename the

pad to match the constraints of your design.

|