# Program Analysis and Compiler Transformations for Computational Accelerators

by

Taylor Lloyd

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

Department of Computing Science

University of Alberta

#### Abstract

Heterogeneous computing is becoming increasingly common in high-end computer systems, with vendors often including compute accelerators such as Graphics Processing Units (GPUs) and Field-Programmable Gate Arrays (FP-GAs) for increased throughput and power efficiency. This thesis addresses the usability and performance of compute accelerators, with an emphasis on compiler-driven analyses and transformations.

First this thesis studies the challenge of programming for FPGAs. IBM and Intel both now produce systems with integrated FPGAs, but FPGA programming remains extremely challenging. To mitigate this difficulty, FPGA vendors now ship OpenCL-based High-Level Synthesis (HLS) tools, capable of generating Hardware Description Language (HDL) from Open Compute Language (OpenCL) source. Unfortunately, most OpenCL source today is written to be executed on GPUs, and runs poorly on FPGAs. This thesis explores traditional compiler analyses and transformations to automatically transform GPU-targeted OpenCL, achieving speedups up to 6.7x over unmodified OpenCL benchmarks written for GPUs.

This thesis next addresses the problem of automatically mapping OpenMP 4.X target regions to GPU hardware. In OpenMP, the compiler is responsible for determining the number and grouping of GPU threads, and the existing heuristic in LLVM/Clang performs poorly for a large subset of programs. We perform an exhaustive data collection over 23 OpenMP benchmarks from the SPEC ACCEL and Unibench suites. From our dataset, we propose a new

grid geometry heuristic resulting in a 25% geomean speedup over geompetries selected by the original LLVM/Clang heuristic.

The third contribution of this thesis is related to the performance of an application executing in Graphics Processing Units (GPUs). Such performance can be significantly degraded by irregular data accesses and by control-flow divergence. Both of these performance issues arise only in the presence of thread-divergent expressions—an expression that evaluates to different values for different threads. This thesis introduces GPUCheck: a static analysis tool that detects branch divergence and non-coalesceable memory accesses in GPU programs. GPUCheck relies on a static dataflow analysis to find thread-dependent expressions and on a novel symbolic analysis to determine when such expressions could lead to performance issues. Kernels taken from the Rodinia benchmark suite and repaired by GPUCheck execute up to 30% faster than the original kernels.

The fourth contribution of this thesis focuses on data transmission in a heterogeneous computing system. GPUs can be used as specialized accelerators to improve network connectivity. We present Run-Length Base-Delta (RLBD) encoding, a very high-speed compression format and algorithm capable of improving throughput of 40GbE up to 57% on datasets taken from the UCI Machine Learning Repository.

#### **Preface**

Chapter 4 has been published as T. Lloyd, A. Chikin, E. Ochoa, K. Ali, J.N. Amaral, "A Case for Better Integration of Host and Target Compilation When Using OpenCL for FPGAs," *Proceedings of the Fourth International Workshop on FPGAs for Software Programmers*, in Sept 2017. I was responsible for identifying transformation opportunities, implementing the device-side transformation of NDRange kernels to single workitem kernels, evaluating the experimental results, and drafting the manuscript. A. Chikin was responsible for implementing pointer restriction and dependence elimination, and drafting the manuscript. E. Ochoa was responsible for implementing the host-side transformation of NDRange to single workitem kernels, implementing the final toolchain, running the experiments, and drafting the manuscript. K. Ali and J.N. Amaral were supervisory authors and contributed to the focus of the final manuscript and to manuscript edits.

Chapter 6 has been submitted for publication as T. Lloyd, K. Ali, J.N. Amaral, "GPUCheck: Detecting CUDA Thread Divergence with Static Analysis." I was responsible for designing, implementing, and evaluating the framework and analysis. K. Ali and J.N. Amaral were supervisory authors and contributed to the experiment design, data analysis, and manuscript edits.

Chapter 5 has been submitted for publication as T. Lloyd, A. Chikin, S. Kedia, D. Jain, J.N. Amaral, "Automated GPU Grid Geometry Selection for OpenMP Kernels." I supervised and guided the data collection and machine learning model design. I analyzed the model created by the machine learning technique and proposed the final heuristic. A. Chikin also supervised data collection and machine learning model design, and drafted the manuscript. S. Kedia performed the machine learning model training and evaluation. D. Jain

performed the initial data collection. J.N. Amaral was a supervisory author, and contributed to manuscript edits.

Chapter 7 was completed in collaboration with IBM Canada and has been submitted for publication as T. Lloyd, K. Barton, E. Tiotto, J.N. Amaral, "Run-Length Base-Delta Encoding for High-Speed Compression." I was responsible for designing, implementing, and evaluating the framework and analysis, and drafting the manuscript. K. Barton and E. Tiotto were IBM collaborators, and participated in manuscript edits. J.N. Amaral was a supervisory author, and contributed to manuscript edits.

#### $To\ Maddy$

For supporting me, marrying me, and listening to my arcane problems.

## Acknowledgements

I'd like to acknowledge my supervisor, Dr J Nelson Amaral, for supporting me throughout my university career, and always having the right advice. Thankyou for the many hours teaching and guiding me.

Thank-you also to Dr Karim Ali, for introducing me to static analysis, and opening me to new perspectives on old topics.

This research has been funded by IBM Center for Advanced Studies (CAS) Canada, the Intel FPGA University program, the government of Alberta, the Natural Science and Engineering Research Council (NSERC) and the University of Alberta. Thank-you all for the essential support.

## Contents

| 1 | Intr                   | roduction                                                                            | 1               |

|---|------------------------|--------------------------------------------------------------------------------------|-----------------|

| 2 | <b>Bac</b> 2.1         | ekground                                                                             | 3               |

|   | 2.1                    | Accelerator Devices                                                                  | 3               |

|   |                        | 2.1.2 Field-Programmable Gate Arrays (FPGAs)                                         | 5               |

|   | 2.2                    | Accelerator Programming Languages                                                    | 6               |

|   | 2.2                    | 2.2.1 CUDA                                                                           | 6               |

|   |                        | 2.2.2 OpenMP                                                                         | 6               |

|   |                        | 2.2.3 OpenCL                                                                         | 8               |

|   | 2.3                    | GPU Divergence Analysis                                                              | 9               |

|   | 2.4                    | Software Compression                                                                 | 10              |

|   |                        | 2.4.1 Lossless Compression                                                           | 11              |

|   |                        | 2.4.2 Parallel Compression                                                           | 12              |

|   |                        | 2.4.3 Compression in Networking                                                      | 12              |

| 3 | Dal                    | ated Work                                                                            | 14              |

| J | 3.1                    | FPGA High-Level Synthesis                                                            | 14              |

|   | 0.1                    | 3.1.1 Manually Optimized OpenCL                                                      | 15              |

|   |                        | 3.1.2 Combined Host/Device Compilation                                               | 16              |

|   | 3.2                    | GPU Parallelism Mapping                                                              | 16              |

|   | 3.3                    | GPU Divergence Analysis                                                              | 17              |

|   | 3.4                    | High-Speed GPU Compression                                                           | 17              |

| 4 | $\mathbf{W}\mathbf{h}$ | Case for Better Integration of Host and Target Compilation en Using OpenCL for FPGAs | 19              |

|   | $4.1 \\ 4.2$           | Introduction                                                                         | 19<br>21        |

|   | 4.2                    | 4.2.1 restrict Pointers to Enable Simultaneous Memory Op-                            | 41              |

|   |                        | erations                                                                             | 21              |

|   |                        | 4.2.2 Prefer Single-Work-Item kernels over NDRange kernels                           | $\frac{21}{22}$ |

|   |                        | 4.2.3 Pipelining Reduction Operations with Shifting Arrays .                         | $\overline{22}$ |

|   | 4.3                    | Compiling OpenCL for FPGAs                                                           | 24              |

|   |                        | 4.3.1 NDRange to Single Work-Item Loop (NDRangeToLoop)                               | 25              |

|   |                        | 4.3.2 Reduction-Dependence Elimination                                               | 28              |

|   |                        | 4.3.3 Restrict Pointer Kernel Parameters                                             | 30              |

|   | 4.4                    | Prototype Performance Study                                                          | 30              |

|   |                        | 4.4.1 Benchmarks                                                                     | 31              |

|   | 4 -                    | 4.4.2 Reduction-Dependence Elimination Efficacy Concluding Remarks                   | 33<br>34        |

|   | 4.5                    | Concurring Remarks                                                                   | .54             |

| 5 | Aut<br>nels | omated GPU Grid Geometry Selection for OpenMP Ker-          |

|---|-------------|-------------------------------------------------------------|

|   | 5.1         | Introduction                                                |

|   | 5.2         | Mapping OpenMP to GPUs                                      |

|   |             | 5.2.1 Nvidia P100 Geometry                                  |

|   |             | 5.2.1 Nvidia P100 Geometry                                  |

|   | 5.3         | Data Collection                                             |

|   |             | Data Collection                                             |

|   |             | to Compiler Default                                         |

|   |             | 5.3.2 Threads Per Block                                     |

|   |             | 5.3.3 Number of Blocks                                      |

|   | 5.4         | Modeling with Machine Learning                              |

|   |             | 5.4.1 Finding Additional Features                           |

|   |             | 5.4.2 Machine Learning Predictor Performance                |

|   | 5.5         | Production Heuristic                                        |

|   |             | 5.5.1 Edge-Case: OpenMP SIMD                                |

|   | <b>-</b> 0  | 5.5.2 Implications of Volta                                 |

|   | 5.6         | Concluding Remarks                                          |

| 6 | GP          | UCheck: Detecting CUDA Thread Divergence with Static        |

|   |             | dysis 5                                                     |

|   | 6.1         | Introduction                                                |

|   | 6.2         | Static Analysis Engine                                      |

|   |             | 6.2.1 Thread-Dependence Analysis                            |

|   |             | 6.2.2 Arithmetic Control Form (ACF)                         |

|   |             | 6.2.3 Inter-procedural Arithmetic Control Form (IACF) 6     |

|   | 6.3         | Detecting Divergent Behaviour                               |

|   |             | 6.3.1 Divergent-Branch Analysis                             |

|   |             | 6.3.2 Non-coalescable Memory Access Analysis                |

|   | 6.4         | An LLVM Prototype for GPUČheck                              |

|   | 6.5         | Evaluation                                                  |

|   |             | 6.5.1 Does GPUCheck provide similar results to dynamic pro- |

|   |             | filing?                                                     |

|   |             | 6.5.2 Do the problems identified by GPUCheck reflect real   |

|   |             | performance opportunities?                                  |

|   |             | 6.5.3 Is GPUCheck performant enough to be used during ac-   |

|   | 0.0         | tive development?                                           |

|   | 6.6         | Concluding Remarks                                          |

| 7 | Rur         | n-Length Base-Delta Encoding for High-Speed Compres-        |

|   | sion        |                                                             |

|   | 7.1         | A New Data Compression Algorithm                            |

|   | 7.2         | RLBD Compression Format                                     |

|   | 7.3         | RLBD Compression and Decompression                          |

|   |             | 7.3.1 Serial Compression                                    |

|   |             | 7.3.2 Serial Decompression                                  |

|   | 7.4         | GPU-Accelerated RLBD                                        |

|   |             | 7.4.1 Parallel Compression                                  |

|   | 7.5         | Evaluation                                                  |

|   |             | 7.5.1 Is RLBD faster than traditional software compression  |

|   |             | schemes?                                                    |

|   |             | 7.5.2 What compression rates are required by modern super-  |

|   |             | computing interconnects?                                    |

|   |             | 7.5.3 Is RLBD compression effective on real-world data? 10  |

|                           | 7.6   | 7.5.4 What throughput improvements can be expected when implementing RLBD? |     |

|---------------------------|-------|----------------------------------------------------------------------------|-----|

| 8                         | Con   | nclusion                                                                   | 106 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | ences                                                                      | 108 |

## List of Tables

| 4.1                      | Benchmark Execution Time and Applicable Transformations .                                                                                                                                                                                                                                                                                                              | 30             |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

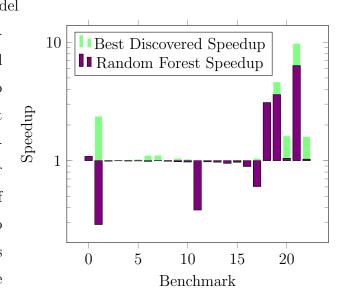

| 5.1                      | Grid Geometry (threads-per-block, blocks) selected for each benchmark by the LLVM selection, our ML model, our proposed heuristic, and exhaustive search. Speedup is shown relative to the LLVM selection. Slowdowns are shown as reciprocals for clarity. Thread-Per-Block values for the Final Heuristic selected using leave-one-out strategy as described in 5.3.2 | 56             |

| 6.1                      | Execution time for GPUCheck vs dynamic profiling. Branches and accesses show the number of instructions requiring ACF analysis over all instructions analyzed                                                                                                                                                                                                          | 83             |

| 7.1<br>7.2<br>7.3<br>7.4 | Identifiers for various possible schema.  Machines Used for performance testing  Datasets used for real-world testing  Common high-speed interconnects, their throughput, and compression/decompression throughput requirements by data savings ratio                                                                                                                  | 87<br>96<br>97 |

|                          |                                                                                                                                                                                                                                                                                                                                                                        | 101            |

## List of Acronyms

**API** Application Program Interface

$egin{array}{ll} \mathbf{B}\Delta\mathbf{I} & \mathrm{Base-Delta\ Intercept} \\ \mathbf{CPU} & \mathrm{Central\ Processing\ Unit} \\ \mathbf{DMA} & \mathrm{Direct\ Memory\ Access} \\ \end{array}$

**DS** Data Savings

FPGA Field-Programmable Gate Array

HLS High-Level SynthesisGPU Graphics Processing Unit

**LUT** Lookup Table

**RLBD** Run-Length Base-Delta

SIMD Same-Instruction Multiple-DataSIMT Same-Instruction Multiple-Thread

SM Streaming Multiprocessor

# List of Figures

| <ul><li>2.1</li><li>2.2</li></ul> | OpenMP 3 example modified from gemm in the Unibench benchmark suite                                                                           | 7                               |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                   | mark suite                                                                                                                                    | 8                               |

| 4.1<br>4.2                        | Altera OpenCL Compilation Flow. From [17] Floating-point reduction sample preventing loop pipelining. From [31]                               | <ul><li>20</li><li>23</li></ul> |

| 4.3                               | [31]                                                                                                                                          | 24                              |

| 4.5                               | pipelining. From [31]                                                                                                                         | 25                              |

| $4.6 \\ 4.7$                      | HelloWorld Kernel. From [2]                                                                                                                   | 27<br>27                        |

| 4.7                               | After NDRange Transformation [2]                                                                                                              | $\frac{27}{27}$                 |

| 4.4                               | Custom OpenCL Compilation Flow                                                                                                                | 28                              |

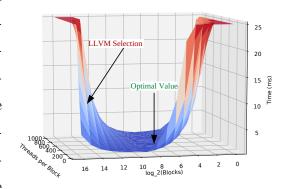

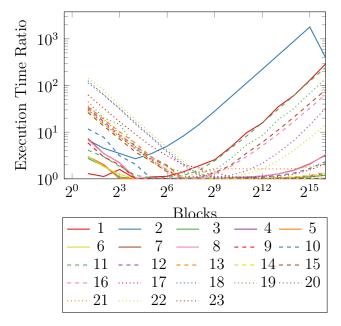

| 5.1                               | Execution time of kernel 21, as a function of the number and size of blocks. The best discovered point is 9.8x faster than the LLVM selection | 37                              |

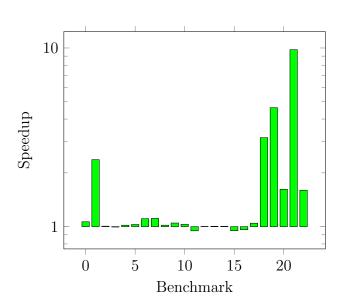

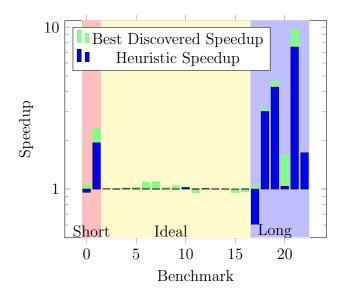

| 5.2                               | Improvement available with the best discovered grid geometry versus the LLVM selection                                                        | 43                              |

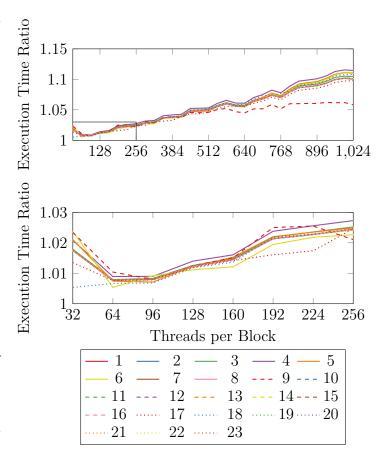

| 5.3                               | Minimum Execution Time at set threads per block / Minimum Execution Time. Each line represents 22 of the 23 benchmarks                        | 44                              |

| 5.4                               | in a leave-one-out manner                                                                                                                     | 44                              |

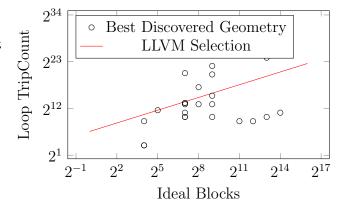

| 5.5                               | Number of blocks minimizing execution time given 96 threads                                                                                   |                                 |

| 5.6                               | per block / Loop Tripcount for each benchmark                                                                                                 | 45<br>49                        |

| 5.7<br>5.8                        | Final Heuristic Algorithm                                                                                                                     | 52<br>53                        |

| 6.1<br>6.2<br>6.3<br>6.4          | Original diffusion coefficient calculation in srad                                                                                            | 59<br>59<br>60                  |

| 6.5              | An example illustrating thread dependence                                | 62  |

|------------------|--------------------------------------------------------------------------|-----|

| 6.6              | An example illustrating if-conversion in $\psi$ -SSA, which serves as    |     |

|                  | inspiration for our ACF analysis                                         | 64  |

| 6.7              | An example illustrating how ACF handles loops                            | 68  |

| 6.8              | An example illustrating the need for Inter-procedural Arith-             |     |

|                  | metic Control Form (IACF)                                                | 68  |

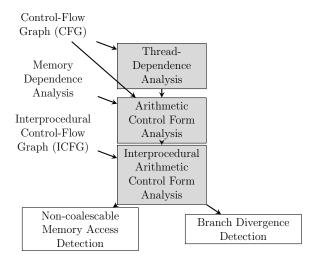

| 6.9              | GPUCheck Analysis Workflow                                               | 70  |

| 6.10             | Coalescing algorithm in GPUCheck                                         | 72  |

| 6.11             | Divergency issues found in the Rodinia Benchmark Suite. Black            |     |

|                  | indicates an issue found only by GPUCheck. White indicates               |     |

|                  | an issue found only by nvprof. Grey indicates an issue found             |     |

|                  | by both. The adjacent fractions are the number of issues found           |     |

|                  | by GPUCheck, over the total issues found                                 | 76  |

| 6.12             | Original gaussian kernel functions (edited for clarity)                  | 79  |

| 6.13             | Extract from lavaMD demonstrating buffering in shared memory.            | 80  |

| 6.14             | Original halo computation in nw kernels                                  | 81  |

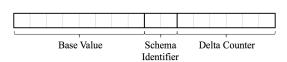

| 7.1              | Configuration of Header for $h = 16$ , $v = 8$ , $s = 2$ , and $c = 6$ . |     |

|                  | Each small light grey box represents one byte                            | 86  |

| 7.2              | RLBD Serial Compression Algorithm                                        | 89  |

| $7.\overline{3}$ | RLBD 1-Lookahead Schema Selection                                        | 90  |

| 7.4              | RLBD Serial Decompression Algorithm                                      | 91  |

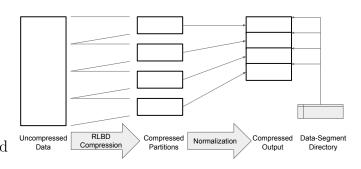

| 7.5              | 2-Stage parallel compression flow                                        | 92  |

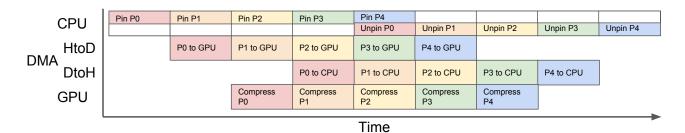

| 7.6              | GPU Compression Pipeline                                                 | 93  |

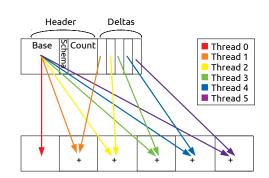

| 7.7              | Visualization of thread-level cooperation within a GPU block             |     |

|                  | during decompression                                                     | 94  |

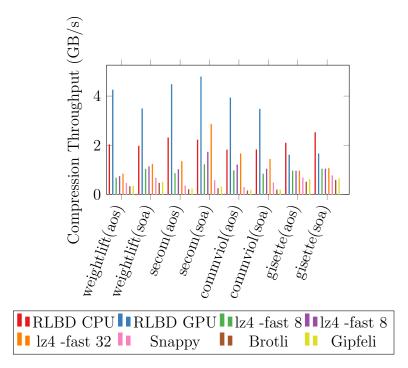

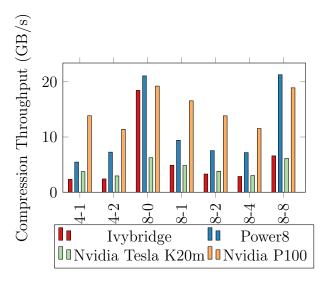

| 7.8              | Compression Throughput by Algorithm on the Sandybridge ma-               | 0 1 |

|                  | chine                                                                    | 98  |

| 7.9              | Throughput of synthetic data compression by schema                       | 99  |

| 7.10             | Throughput of synthetic data decompression by schema                     | 99  |

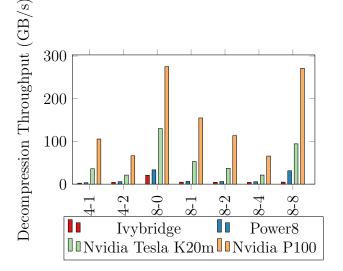

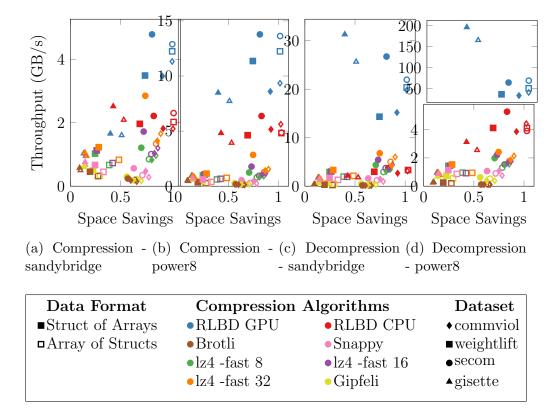

| 7.11             | Throughput vs Data Savings                                               | 102 |

## Chapter 1

### Introduction

Heterogeneous computing platforms are emerging as the dominant approach to supercomputing. GPUs have become an increasingly popular choice in achieving a superior performance per watt ratio with some of the highest absolute performance. In the most recent Top500 list [66], six out of the top ten machines use accelerator devices. The third fastest machine - the Swiss National Supercomputing Centre's Piz Daint, for example, delivers its performance with 5,320 NVIDIA Tesla P100 GPUs. The upcoming Summit supercomputer, to be deployed at the Oak Ridge National Laboratory, is set to lead the TOP500 list in 2018 with slated peak performance of 200 petaflops from more than 25,000 NVIDIA V100 GPUs coupled with 9,200 IBM POWER 9 CPUs [50]. By coupling GPUs to each node, Summit aims to deliver over 200 petaflops in a power envelope of 10 MW, a five-fold increase over the performance of the previous Titan supercomputer while consuming only 10% more energy. Providing even more power efficiency than GPUs, Field-Programmable Gate Arrays (FPGAs) are beginning to ship in high-end server hardware. Intel is now shipping Xeon server CPUs with an integrated FPGA, and IBM ships System Z machines with a built-in FPGA. These devices are required to achieve necessary performance requirements while consuming less power than traditional CPU-centric systems.

Hardware accelerators such as GPUs and FPGAs can dramatically improve application performance, but require different programming paradigms for efficient execution. GPUs execute thousands of threads simultaneously,

interleaving thread execution to hide instruction latency. FPGAs execute spatially, using deep pipelining to efficiently process tasks. Both models map poorly to traditional programs optimized for a sequential CPU.

Further complicating accelerator programming, both GPUs and FPGAs maintain internal memory, and must manage copying of relevant data to and from the accelerator device. Accelerators are typically connected via a PCIE bus or equivalent, so for many computations data transfer can actually dominate execution time.

To simplify accelerator programming, compiler and language designers have taken two approaches, creating new programming languages like CUDA, OpenCL, OpenMP, and OpenACC. CUDA and OpenCL present programmers a low-level abstract machine model, allowing developers to take advantage of architectural characteristics by hiding few device-specific details. By contrast, OpenMP and OpenACC encourage programmers to express parallelism in their programs, but provide few machine details. In these languages, the compiler is responsible for mapping parallelism to the appropriate architectures, with the goal of hiding architectural details and achieving performance portability into the future.

This work leverages both styles of accelerator languages, applying compiler analyses and transformations to take better advantage of GPUs and FPGAs. This work is a compilation from a number of projects, each presented independently by chapter. Chapter 4 presents compiler transformations for OpenCL when targeting FPGAs, by combining host and device analysis. Chapter 6 presents a compiler analysis for CUDA programs to detect memory access patterns and conditional branches which may cause performance problems when executing on GPUs. Chapter 5 presents a compiler heuristic for mapping OpenMP-parallel programs to GPUs to maximize performance. Finally, Chapter 7 presents a novel compression algorithm, Run-Length Base-Delta (RLBD) originally intended to compress CPU-GPU data transfers. Unfortunately, performance was insufficient for the intended use, but RLBD can be used with GPU acceleration to improve supercomputing network performance.

### Chapter 2

## Background

#### 2.1 Accelerator Devices

This body of work concentrates on GPUs and FPGAs, two specific accelerator devices.

#### 2.1.1 Graphics Processing Units (GPUS)

GPUs are composed of tens to hundreds of streaming multiprocessors (SMs), each capable of independently executing thousands of threads in parallel. To efficiently load and execute code on such devices, a shared program kernel is executed by many threads at once, in a data-parallel fashion. When executing a kernel on a GPU, threads are grouped into thread blocks. All threads within a thread-block execute on a single streaming multiprocessor (SM), and are therefore able to perform cooperative tasks and share intermediate products. By contrast, threads in different thread-blocks cannot communicate directly. The number of thread-blocks and the number of threads per block are collectively referred to as a grid geometry and they both must be specified when initiating a kernel execution.

Each SM is a highly vectorized processing unit, capable of executing an instruction for a warp of 32 threads each cycle. All threads within the warp must execute the same instruction, as each SM has only a single instruction decoder. To hide instruction latency, the SM is fully pipelined and executes a different warp of threads each cycle, using zero-cost context switching. The GPU achieves zero-cost context switching by simultaneously holding registers

for each thread in a common register file, and using the thread ID as an offset. Each SM has hardware limits to the number of threads that can be simultaneously loaded and executed: In addition to the register file having finite capacity, each SM can hold only a finite number of threads (1024 on the Nvidia P100) and finite number of blocks (32).

Modern NVidia GPUs issue each instruction to a warp of 32 threads simultaneously: All threads in a warp must execute the same instruction each cycle. Branch divergence occurs when a conditional branch instruction is issued to a warp and the condition evaluates to a different value for some threads within the warp. In this case, the hardware must first execute the code in the taken path—leaving idle the threads that evaluate the condition to false—and subsequently it must execute the not taken path while leaving idle the threads that evaluate the condition to true. All threads may continue executing when the control flow reconverges at the join point in the flow graph. Such underutilization of processing resources reduces the performance of GPUs. Branch divergence is problematic because stalled threads are still assigned registers and execution slots, preventing other threads from being started to perform useful work.

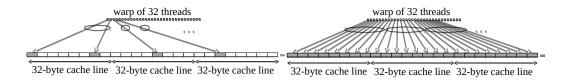

A warp of threads issues instructions simultaneously, causing as many as 32 simultaneous memory access requests to be issued in one execution cycle. However, the bandwidth available to access a GPU global memory subsystem is limited. Thus, the hardware in a GPU is able to coalesce (merge) adjacent or overlapping requests that originated on the same cycle by threads within a warp into fewer requests, each accessing more data. Once a memory access request is issued, no threads in a warp can continue executing until all of the threads have been serviced. Therefore, coalescing multiple memory accesses into fewer requests dramatically improves throughput. However, the hardware is only able to coalesce requests if the threads in a warp are accessing adjacent or overlapping locations in memory, and if the range of accessed addresses is aligned to a cache line boundary. If the execution of a statement leads threads to access memory locations that do not fit within an aligned range of memory addresses, then multiple memory requests are necessary. Therefore,

the execution time is longer than in the case where all the accesses for the warp are coalesced into a single request. Each global memory request requires hundreds of cycles to be completed. Thus, GPU programs should be structured to avoid non-coalescable memory accesses.

All SMs share a common global memory, using local caching to reduce latency. The global memory is also attached to a Direct Memory Access (DMA) controller, which can transfer memory between global GPU memory and CPU memory without requiring either the CPU or GPU SMs for processing. The DMA controller allows memory transfers to and from the GPU to be overlapped with GPU processing.

Despite the increased reliance on GPUs, the structured style of parallel processing that GPUs require makes their performance sensitive to two problems: (1) branch divergence [22], in which adjacent threads exhibit different control-flow behaviour causing hardware stalls, and (2) non-coalesced memory accesses [8], in which adjacent threads access disparate memory addresses, overloading the underlying memory system with requests.

#### 2.1.2 Field-Programmable Gate Arrays (FPGAs)

FPGAs consist of arrays of interconnected programmable logic blocks, which vary in complexity from simple lookup tables (LUTs) to complete functional units. LUTs can be wired up via programmable interconnects to form arbitrary digital circuits.

Typically, circuit configuration is specified via a Hardware Description Language (HDL) such as Verilog or VHDL. The HDL is then compiled into a 'bit-stream' - a configuration file that sets the device's logic blocks and interconnect switches into a desired state. The compilation process consists of placing circuits specified by user HDL code to the chip, while considering chip area usage and interconnect length/congestion. The placed circuits then undergo routing, i.e., adding wires to correctly connect the placed components. Arriving at an optimal circuit configuration is a known NP-hard problem. Synthesis takes from hours to days.

#### 2.2 Accelerator Programming Languages

#### 2.2.1 CUDA

CUDA is a parallel programming API created by Nvidia to allow developers to tightly integrate with their GPUs. Functions written in C/C++/Fortran can be marked for GPU execution and called by CPU (host) code, while the CUDA compiler handles compiling and linking GPU executables.

Parallelism in the CUDA programming model is of a SIMT (Single Instruction Multiple Thread) form. In CUDA, a program is divided into host code and a series of *kernels*. The code for each kernel describes the execution of a single thread, but the programming model assumes that many threads will execute that same kernel code in parallel. Threads are grouped into blocks, and a number of blocks are executed simultaneously. The number of threads per block and the number of blocks are collectively referred to as a grid, and must be specified each time a kernel is executed.

CUDA is meant to enable tight integration with GPUs, and therefore exposes many GPU-specific features through the addition of new keywords and intrinsics. In particular, CUDA exposes the threadIdx and blockIdx variables, which expose the thread numbers during execution, and allow programmers to create thread-dependent behaviour. Because GPUs execute threads in warps of 32, Nvidia also exposes intrinsics to allow threads within a warp to cooperate at no cost through intrinsic functions like ballot(c) which takes a predicate from each thread, and returns a 32-bit binary value combining all of the predicates.

By enabling tight coupling of programs to GPUs, CUDA seeks to enable high-performance GPU computing through deep programmer knowledge and understanding.

#### 2.2.2 OpenMP

OpenMP [18] allows programmers to mark sections of code as parallel without worrying about how such parallelism maps to hardware. However, since high-level programming models like OpenMP abstract the architecture-specific details of code generation, accelerator offloading functionality exacerbates an age-old problem of such models: compilers must attempt to optimally map parallelism to each targeted architecture.

#### OpenMP is a prescriptive

directive-based programming frame- 1 void gemm\_OMP work, and an API designed for both shared and distributed memory multiprocessing programming using C, C++, and FORTRAN. It is made up of a collection of compiler directives for controlling execution of a parallel application, library routines for interfacing with 13 } the runtime environment, and environment variables. Figure 2.1 Figure 2.1: Open shows an example taken from the gemm benchmark where the programmer annotated the loop on

```

(float *A, float *B, float *C) {

#pragma omp parallel for

for (i = 0; i < NI; i++) {

for (j = 0; j < NJ; j++) {

5

C[i*NJ + j] *= BETA;

6

for (k = 0; k < NK; ++k) {

7

C[i*NJ + j] +=

8

9

ALPHA * A[i*NK + k]

*B[k*NJ + j];

10

}

}

}

14 }

```

Figure 2.1: OpenMP 3 example modified from gemm in the Unibench benchmark suite

line 4 with the parallel for directive, instructing the compiler that iterations of that loop may be executed in parallel, though the inner loop on line 5 must still be executed serially. The compiler generates code to create worker threads that will execute in parallel and divides a work task among the worker threads. However, it is up to the runtime environment to allocate threads to different processors. This programming model abstracts details of worksharing and thread coordination and allows programmers to focus on solving the task at hand. Moreover, the high level of abstraction makes OpenMP highly portable, promising, in principle, code scalability from standard workstations to supercomputers. However, because compiler heuristics can be suboptimal, OpenMP designers included syntax for programmers to provide hints to the compiler to attempt to improve performance for a given target architecture. The OpenMP language specification has accumulated considerable bloat to accommodate such hints. Still, the goal of portability of OpenMP through

more efficient mapping of parallelism to hardware has attracted considerable attention [51], [73].

#### OpenMP 4.x Target Offloading

```

15 void gemm_OMP

(float *A, float *B, float *C) {

#pragma omp target

map(to: A[:NI*NK], B[:NK*NJ])

18

map(tofrom: C[:NI*NJ])

19

#pragma omp teams distribute

20

parallel for

for (i = 0; i < NI; i++) {

21

for (j = 0; j < NJ; j++) {

22

C[i*NJ + j] *= BETA;

23

for (k = 0; k < NK; ++k) {

24

C[i*NJ + j] += ALPHA * A[i*NK]

25

+ k]

26

* B[k*NJ +

j];

}

27

28

}

29

30 }

```

Figure 2.2: OpenMP 4 example simplified from gemm in the Unibench benchmark suite

OpenMP 4.0, introduced in 2014, allows programmers to specify target regions blocks of code to be executed on an accelerator device present in the system. Variables are mapped to the device data environment and the code generation for parallel constructs enclosed in the target region targets the accelerator architecture. Figure 2.2 shows the same parallel segment of the gemm benchmark as Figure 2.1, but targeting OpenMP 4.0. The target region is declared

on line 17, causing the entire loop nest to be executed on the GPU. Lines 18-19 show the data mapping of the arrays, making them available within the target region. Finally, the outermost loop is made parallel as before on line 20. The additional teams distribute clause indicates that these loop iterations should first be divided amongst teams, and then amongst threads within each team.

#### 2.2.3 OpenCL

OpenCL is an open standard for parallel programming of heterogeneous systems and a programming language specification [26]. General OpenCL program architecture consists of a host device that controls one or multiple com-

pute devices by managing memory transfers and task distribution across devices. Compute devices are split into compute units, which, in turn, contain individual processing elements. OpenCL defines a Same-Instruction Multiple-Thread (SIMT) data-parallel model where many threads execute the same instruction on many data items. In OpenCL terminology this model is called *NDRange* (for N-dimensional range). OpenCL also provides task-level parallelism that exploits concurrency through stand-alone task distribution across different compute units.

The main purpose of OpenCL is to enable portable use of various hardware accelerators. While already popular for GPU accelerators, recent adoption of the framework as an High-Level Synthesis (HLS) input language has opened new opportunities to explore FPGA-specific compiler transformations.

#### 2.3 GPU Divergence Analysis

Automated tools exist for most programming languages to detect common programming mistakes [7], [11], [36]. Such tools make use of static analysis techniques to verify correct program behaviour. We focus this section quite narrowly, highlighting prior work on detecting branch divergence and non-coalescable memory accesses for GPU kernels.

Sampaio et al. [58] propose a conservative divergent-branch analysis over affine expressions on thread identifiers, now implemented within LLVM. An extension to their work generalizes to divergent values throughout a GPU kernel. In contrast, GPUCheck does not require affine expressions, and can solve for non-linear conditions. Moreover, GPUCheck derives divergent expressions from arbitrary control-flow and data dependencies even across interprocedural boundaries.

Transforming non-coalescable memory accesses into coalesced accesses has been an active subject of research. Wu et al. [74] show that given perfect knowledge of memory access layouts, minimizing non-coalesced accesses is an NP-hard problem. However, the authors do not consider what analysis might be used to generate such layouts. GPUCheck is well-suited to perform such

a task. Affine polyhedral models have also been used to transform memory accesses [5], [71]. Venkat et al. [70] have recently extended the polyhedral model to include limited non-affine expressions. While GPUCheck cannot currently perform transformations, it identifies non-coalesced accesses, even when generated indirectly through multiple function invocations. Additionally, GPUCheck calculates memory access patterns simultaneously for data- and control-flow dependent values.

Fauzia et al. [19] present an approach that requires dynamic analysis to identify non-coalesced accesses using memory traces. Their work generates high-accuracy results, but requires any kernel to be executed, suffering from the same issues as any dynamic profiler. On the other hand, GPUCheck runs its analysis without even a GPU present, by calculating inter-thread behaviour.

#### 2.4 Software Compression

Data compression schemes allow for data to be represented with fewer bytes, which is valuable both to reduce storage requirements and to transmit data at higher speeds. However, when considering the transmission of compressed data, one needs to also consider the compression and decompression operations that must occur at each end. More effective compression schemes tend to require more computation, reducing the maximum throughput at which they can operate. Compression schemes therefore exist along a spectrum, where incrementally more computation can result in incrementally smaller compressed data. Over recent years, network and interconnection link speeds have been increasing faster than compute and memory speeds. With faster networks, in order for a compression scheme to be advantageous, it must require less compute resources.

Software compression schemes such as brotli [1], gipfeli [40], lz4 [12] and Snappy [24] achieve impressive compression ratios across a wide sample of data at rates up to hundreds of Mbits. Meanwhile, simple compression schemes such as Base-Delta Intercept ( $B\Delta I$ ) achieve limited compression, but are simple enough to be implemented in hardware at rates of up to hundreds of Gbits [54].

Data compression schemes are divided into two categories: lossy and lossless. Lossy compression schemes are allowed to discard information to reduce file sizes, and are used when exact replication of the compressed data is not necessary. Lossy compression is commonly used, for example, to compress JPEG images and MP3 audio. By contrast, lossless compression schemes must reproduce the exact input through decompression. Compression schemes represent a trade-off between compression ratio and computational requirements.

A compression ratio is a measure of the degree to which a compression scheme reduces the size of a piece of data, and is defined as  $size_{original}/size_{compressed}$ . The reciprocal of the compression ratio is known as  $space\ savings$ .

Throughput is a measure of the speed of compression and decompression, and is measured in bytes/sec. Typically compression and decompression rates are reported separately because decompression is usually much faster than compression.

#### 2.4.1 Lossless Compression

Lossless compression is required in many cases, such as when transmitting files in ZIP format, where an inexact reproduction could result in data corruption. In particular, whenever compression is intended to be hidden from users, lossless compression is required. Two well-known lossless compressions are Run-Length Encoding (RLE) and Lempel-Ziv Compression (LZ).

RLE is a simple compression scheme that encodes repeated values using a sentinel value (typically a value repeated twice) followed by a count. These repeated values, known as runs, are thus compressed. Variations exist with regard to the size of each value, and the method of encoding runs. Run-length encoding is extremely simple to implement, and has even been implemented in hardware. Fax machines notably implement RLE for lines of color during transmission over telephone lines. While trivial to implement, RLE is ineffective when the incoming data does not contain long sequences of identical values.

Lempel-Ziv compression uses the intuition that a recently used value is likely to be reused. A sliding window of history is maintained during compression, and if an encountered value or sequence is present in the history window, it is replaced with a code word in the compressed output. During decompression, the same history window is constructed, such that the code words can be decoded by referencing the window. Many variations on LZ exist, varying the size of values and the size of the history window. Most commonly used today is the LZ4 algorithm [12].

#### 2.4.2 Parallel Compression

Given the general availability of multicore processors, efforts have been made to parallelize software compression algorithms. Parallel compressors tend to either partition the input into segments for separate compression [45], or apply cooperative parallel algorithms. They often achieve sublinear scaling [35], [62].

For GPU parallelism, Sitaridi et al. introduced Gompresso [63], a GPU algorithm for decompression. Gompresso splits an input file into partitions and independently compresses each partition with LZ77, a Lempel-Ziv variant. Gompresso achieved decompression speeds of up to 16 GB/s on an Nvidia Tesla K40 by exploiting GPU parallelism. However, their algorithm sacrifices compression ratios, and does not investigate compression throughput.

Others have attempted to use GPUs to offload portions of a compression algorithm. Shastry et al. use a GPU to perform the Burrows-Wheeler transform in bzip2 compression [61], improving bzip2 throughput by 44% while leaving the CPU idle half of the time, and thus allowing other operations to continue.

#### 2.4.3 Compression in Networking

There is a long history of using compression to improve network throughput. Craft used a variant of LZ compression implemented in hardware to achieve throughputs of up to 1 Gb/s in 1998 [14]. More recently, and more commonly, HTTP connections support compression to dramatically reduce webpage load time [42].

However, modern data centres and supercomputers are connected by fabrics operating at 10-40 Gb/s. Therefore, most software compression schemes

in use today cannot keep up with the volume of incoming or outgoing data.

### Chapter 3

#### Related Work

As this work is a compilation of multiple research projects, related work is divided here by project.

#### 3.1 FPGA High-Level Synthesis

Czajkowski et al. present an LLVM-based OpenCL compiler prototype for Altera FPGAs, with a proof of concept executing on the Stratix DE4 [17]. This compiler represents all basic blocks of the program as Control-Data Flow Graphs (CDFG) with their own inputs and outputs as determined through livevariable analysis. The CDFG allows for efficient implementation of a module as a pipelined circuit, as opposed to finite state machine with a datapath - an approach much better suited to the data-parallel OpenCL model. This compiler implements the NDR ange execution model by issuing individual work items into a kernel pipeline, one after another. The task-parallelism execution model, where the kernel code is written in a serial fashion, is implemented in the compiler by attempting to pipeline every loop in the code. The compiler also creates a wrapper for the generated kernel circuits to handle the standard interfaces to the device-memory IO and does all necessary bookkeeping to track kernel execution and to issue new work-itemss into the pipeline. This work subsequently became the Intel FPGA OpenCL compiler, upon which our optimizations are based. Internally, the compiler consists of an LLVM-based HLS component that compiles OpenCL kernel code into Verilog, which is then synthesized using standard Intel FPGA Quartus software.

Intel FPGA also provides an implementation of the OpenCL API to allow host code to interface with devices: launch kernels, manage memory transfers, etc.

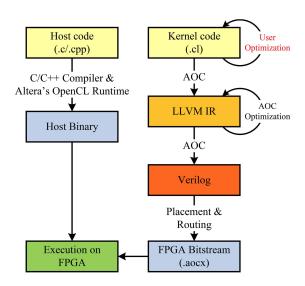

Figure 4.1 depicts the compilation flow as provided by Intel FPGA. A typical execution workflow consists of the host code programmatically loading a pre-compiled kernel binary file into the FPGA and initiating its execution. Intel FPGA also provides custom extensions to the OpenCL standard enabling certain architecture-specific user optimizations. While the prototype described here uses the Intel FPGA OpenCL toolchain targeting a Stratix V FPGA, the general concepts are applicable to reconfigurable architectures of other FPGA vendors.

As of 2015, Xilinx SDAccel development environment provides a HLS toolchain that is fully compliant with OpenCL 1.0. SDAccel is a closed-source application and little is known about its inner workings. We can infer from the user guide that the data-parallel NDRange execution model in this compiler is emulated through generation of a 3-dimensional loop-nest that iterates over the work-group and work-item dimensions [59]. Loop pipelining is one of the essential optimizations attempted by SDAccel [21]. SDAccel would also provide a good platform to prototype the analyses and transformations.

#### 3.1.1 Manually Optimized OpenCL

Writing OpenCL code that delivers good performance on FPGAs is an open problem. Intel publishes a best-practices guide [31] detailing strategies and patterns that the Intel FPGA OpenCL compiler can efficiently execute. These patterns served as inspiration for the transformations presented in this paper. Zohouri et al. [77] performed manual optimizations on six Rodinia OpenCL benchmarks compiled with the Intel FPGA OpenCL compiler. After these optimizations, FPGAs could be competitive with GPUs on performance with dramatically better power efficiency. The effectiveness of these transformations inspired our compiler transformations.

#### 3.1.2 Combined Host/Device Compilation

Lee et al. [38] developed an OpenACC-to-FPGA compiler framework, that converts OpenACC programs into OpenCL using the open-source OpenARC compiler, and then uses the Intel FPGA OpenCL compiler for HLS. The approach benefits from the fact that user-level source code contains device kernel code embedded into the host control code. This source code is annotated with pragmas that specify the code blocks that are offloaded to the device. Before the device code is outlined into a separate OpenCL kernel compilation unit, their compiler is able to take advantage of certain code-transformation opportunities that would not have been possible otherwise, such as bypassing global memory for inter-kernel communication using channels. To the best of our knowledge, our work is the first to implement combined compilation on OpenCL source code exposing similar transformation opportunities.

#### 3.2 GPU Parallelism Mapping

Tuning of compile-time and launch-time kernel parameters of GPGPU code has attracted considerable research in light of GPUs' popularity. Vollmer et. al. presented an approach to construct auto-tunable GPU kernels by expressing them in an embedded DSL [72]. The abstractions enforced by the DSL both restrict the parameter search spaces, and allow the use of common search strategies. Lee et. al. developed OpenMPC - an extension to OpenMP for generation of parallel GPU code before OpenMP 4.0 was announced [39]. Their work allowed for auto-tuning of generated CUDA code through a search of the optimization space, but left the number of threads and number of blocks to be specified explicitly by the user through additional pragma directives. A similar work by Grauer-Gray, on GPU code generated from a high-level HMPP language, applied auto-tuning on a large optimization space that targeted GPU kernels [25]. Their approach hard-coded fixed GPU geometries that aimed at maximizing occupancy.

To the best of our knowledge, our work is the first to investigate automatic selection of Grid Geometry in the context of OpenMP GPU kernels.

Multiple applications of automated learning to parallel systems appear in the literature. Wang et. al. use neural networks to map parallelism of OpenMP 3 programs to NUMA computing clusters [73]. In the domain of heterogeneous computing systems; O'Boyle et. al. use a predictive modeling approach to select parallel OpenMP 3 loops for translation to OpenCL GPU kernels [51]. Tournavitis et. al., in the context of auto-parallelizing compilers, use a machine learning model to map parallelism to hardware while profiling, with the goal of maximizing the information collected [67].

Coons et. al. attempt to use instruction-placement heuristic algorithms powered by reinforcement learning technique to reduce communication overhead on Explicit Dataflow Graph Execution processors [13]. While their learning approach produces models that match expert hand-tuned heuristics, it lacks generality. To compensate for the highly-specialized nature of the learned models, they propose a hierarchical approach where units of code are classified into groups that perform well with similar heuristics, using the same learning model for classification. They observe that even when machine learning and data mining techniques are impractical, these methods can still deliver valuable insights to a compiler designer.

#### 3.3 GPU Divergence Analysis

Previous attempts to analyze GPU workloads observe dynamic behaviour on either a simulator [4] or on physical GPUs [8]. These analyses produce precise results, but come at a cost. To benefit from dynamic analysis, the application developer must have access to GPUs with similar characteristics to the target system, or experience substantial overheads to simulate GPU execution.

#### 3.4 High-Speed GPU Compression

Few attempts have been made to implement lossless compression on GPUs, mainly due to the negative effect on compression ratios caused by partitioning. Patel *et al.* implemented a bzip-like cooperative GPU compression algorithm, but found performance was actually slower than the CPU-based bzip2 algo-

rithm [53]. Ozsoy et al. implemented a partitioned LZ compression algorithm on GPUs, and achieved a performance throughput 2.2x higher than their parallel CPU algorithm [52]. These works both leave substantial room for a compression algorithm designed for efficiency on a GPU architecture.

## Chapter 4

## A Case for Better Integration of Host and Target Compilation When Using OpenCL for FPGAs

#### 4.1 Introduction

This work seeks to take OpenCL programs meant for GPU execution, and apply compiler analysis and transformations to enable more efficient FPGA execution.

OpenCL [64] has emerged as a prominent programming model for FPGA. Intel and Xilinx release OpenCL compiler toolchains that support hardware synthesis directly from OpenCL source [17], [21]. GPU-targeted programs rarely achieve acceptable performance when run unmodified on FPGAs [77], so new FPGA-specific compiler techniques and insights are required.

In contrast to the data-parallel model favoured by GPUs, Intel FPGA HLS tools follow a different approach when implementing the NDRange model: synthesized kernels execute instructions in a pipelined fashion, similar to that of an assembly line. In an FPGA, this means that a data processing unit (e.g. a logic block) takes as input the output of a previous data processing unit. These units can perform concurrent computation because their work is independent from each other. The reconfigurable fabric on FPGAs makes SIMT parallelism a poor choice for applications. The pipeline parallelism

model improves utilization by requiring fewer copies of each operator, while maintaining overall throughput [28].

A major feature of OpenCL is separate host and device compilation, allowing OpenCL device vendors to specialize in device-code generation without concern for host implementations. This separation enforces strict Application Programming Interface (API) boundaries between host and device implementations and prevents otherwise trivial compiler optimizations and analyses. As a result, workarounds must be introduced to recover lost performance.

For example, Intel FPGA extends

Figure 4.1: Altera OpenCL Compilation Flow. From [17].

the OpenCL specification with *channels* that allow kernel operations to be chained without needing to copy back to memory. If a compiler had access to the combined host and device code, chaining would be a trivial example of loop fusion. However, with kernel definitions compiled separately from invocations, programmers must implement additional APIs to realize the benefits of chaining.

This work builds on existing work by Zouhouri et al. [77] that analyzes and improves the performance of GPU-targeted OpenCL kernels on Intel FPGA devices using the Intel FPGA SDK for OpenCL. This paper expands compiler analyses to include both host and device compilation and introduces compiler transformations that benefit from sharing analysis information between the host and device compilation. In particular, we define three compiler transformations that transform OpenCL kernels to more closely match the best-practices published by Intel FPGA:

NDRange to Loop: Convert NDRange kernels, originally intended to be

repeatedly executed with a range of thread identifiers (IDs), to a single body of code that uses a loop induction variable to represent thread IDs.

**Restrict Parameters:** Improve device-side alias analysis by inspecting host code and by marking kernel parameters with the **restrict** attribute where applicable.

While the above two transformations take advantage of the host and device compiler information sharing; they also enable the compiler to optimize the kernel code further by applying single-work-items-specific transformations, such as:

**Reduction-Dependency Elimination:** Improve pipelining of reduction loops by storing partial sums in a shift register to reduce loop-carried dependencies.

These transformations integrate with the Intel FPGA SDK for OpenCL and are evaluated on the Rodinia benchmark suite [10]. Rodinia benchmark OpenCL implementations target GPU-like devices and, as such, are an appropriate baseline for FPGA-specific transformations.

#### 4.2 Optimizing OpenCL for FPGAs

Intel FPGA maintains a best practices guide for writing OpenCL that will execute efficiently on FPGAs [31]. A subset of these optimizations motivate the remainder of the work, and are summarized here.

# 4.2.1 restrict Pointers to Enable Simultaneous Memory Operations

FPGAs improve performance by executing multiple operations simultaneously. However, memory operations are defined to behave as if performed in program order, and can have extremely long latencies. If two memory accesses never reference the same memory address, then the compiler can safely reorder or overlap the operations. By marking a pointer passed as kernel parameters with

restrict, programmers guarantee that any address accessible through that pointer is inaccessible through any other pointer. The Intel FPGA OpenCL compiler can then perform other memory operations simultaneously. As kernel parameters are passed opaquely from the host to the FPGA, it is otherwise extremely difficult for the compiler to prove that memory operations are safe to overlap. Memory operations require hundreds of FPGA cycles, so overlap is required for an efficient pipeline.

## 4.2.2 Prefer Single-Work-Item kernels over NDRange kernels

In an NDRange kernel, the same computation is executed by a large number of threads to support the data-parallel model. On FPGAs, chip area constraints prevent massively parallel processing units from being constructed. Instead, NDRange kernels are pipelined on FPGAs, allowing the stages to be executed concurrently such that subsequent threads can be started each cycle. All threads are executed in a single shared pipeline and thus values that do not differ between threads can be calculated once, and referenced from within the pipeline. However common intermediate products cannot be expressed in NDRange kernels, so single-work-items kernels are preferred.

Moreover, loops in NDRange kernels would have to be fully unrolled to support efficient pipelined execution because a pipeline is constructed across thread invocations. By converting an NDRange kernel to a single work item, loop exchange can generate pipelines where not otherwise possible. This conversion can also enable new transformations such as shift register reduction (described next). The effectiveness of the pipelined execution model depends on the target algorithm. Algorithms with little synchronization or control-flow may not benefit from single work-items execution at all and will have better performance with NDRange kernels.

# 4.2.3 Pipelining Reduction Operations with Shifting Arrays

The performance of the single work-item execution model depends on the ability to pipeline loops in the kernel code. Thus, removing loop-carried dependencies is especially important because such dependencies induce longer loop initiation intervals. Reduc-

Figure 4.2: Floating-point reduction sample preventing loop pipelining. From [31].

tion operations, such as the double\_add\_1 method shown in Figure 4.2, cannot be pipelined well because the intermediate value temp\_sum must be computed for each iteration before the next iteration can begin. Floating-point operations are relatively slow, causing the FPGA to stall for the majority of the computation. Addressing a similar problem in the context of software loop pipelining in 1992, Rau et al. [55] first introduced a technique called modulo scheduling that employs a rotating register file as a means to achieve a more compact loop schedule and thus reduces the loop initiation time. This technique was later implemented in hardware in the Intel IA-64 architecture [60].

As suggested in the best-practices guide [31] and implemented by hand by Zouhouri et al. [77], a variation of the rotating register technique can be employed by the programmer manually to minimize pipeline delays caused by the intermediate value in a reduction operation. Figure 4.3 shows the same reduction, but with the introduction of a local array to emulate a shift register. Instead of reducing elements of arr into a single variable, they are accumulated into a shift register. The shift register's depth is equal to the latency, in cycles, of the floating-point operations that form the dependency. Reduction input is read from the first element of the shift register, and written into the last. Effectively, this reduces the initiation interval of the loop to 1 cycle. After the loop completes, an extra reduction on the shift register contents produces the final reduction value. Because the final shift register summation loop has a smaller trip count, the improved initiation interval of the original loop yields an overall performance improvement. The Intel FPGA

OpenCL compiler looks for the pipelining idiom from Figure 4.3 in OpenCL code, and efficiently implements it using a shift register in hardware.

## 4.3 Compiling OpenCL for FPGAs

The transformations suggested in the Intel FPGA best-practices guide are meant to be performed by programmers. However, a sufficiently capable compiler should be able to automatically transform OpenCL device code to deliver more efficient execution on FP-GAs. Thus, we integrated some of the transformations into the Intel FPGA SDK for OpenCL compiler. This compiler is a closed-source application based on the LLVM compiler infrastructure. Thus, arbitrary compiler passes targeting

```

__kernel

2 void double_add_2(__global double *arr, int

__global double *result)

4 {

double shift_reg[II_CYCLES+1];

//Initialize all elements of shift_reg to

for(int i = 0; i < N; ++i)

shift_reg[II_CYCLES] = shift_reg[0]+arr[

i];

#pragma unroll

for(int j = 0; j < II_CYCLES; ++j)</pre>

shift_reg[j] = shift_reg[j+1];

13

double temp_sum = 0;

14

15

16

#pragma unroll

for(int i = 0; i < II_CYCLES; ++i)</pre>

18

temp_sum += shift_reg[i];

19

*result = temp_sum;

20 }

```

Figure 4.3: Floating-point reduction using a shift register to enable loop pipelining. From [31].

LLVM 3.0 can modify the Intermediate Representation (IR) .

Our transformations are performed early in the compilation process because they attempt to automate best practices when writing source code. OpenCL is designed to allow for the separate compilation of host and device code. However, combined compilation allows for optimizations not previously possible. Moreover, the Intel FPGA compiler already requires some degree of such coordination by the user. For instance, the compiler may generate single-work-item code for a kernel that the host invoked in NDRange mode. Our compiler passes make use of coordination between the host and device code compilation processes, passing information between the two to enable certain transformations. A custom compiler driver facilitates combined compilation, accepting as input the host and device source-code files. The driver

```

size_t work_dim = 2;

size_t gbl_offset[2] = {0, 0};

size_t gbl_size[2] = {64, 8};

size_t lcl_size[2] = {32, 1};

clEnqueueNDRangeKernel(

cmd_queue, kernel, work_dim,

gbl_offset, gbl_size, lcl_size,

wait_list_size, wait_list, event);

```

Figure 4.5: Host NDRange kernel invocation

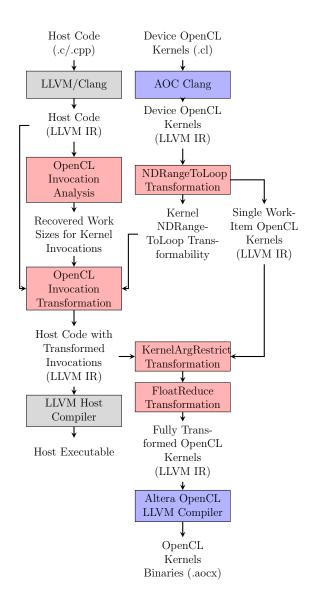

coordinates between the Intel FPGA compiler modified with our transformations and the host compiler, based on LLVM 4, with modifications to analyze and transform host-to-device communication. To integrate our three transformations with the Intel FPGA OpenCL Compiler, the host code analyses are choreographed with the device code transformations (Figure 4.4).

# 4.3.1 NDRange to Single Work-Item Loop (NDRange-ToLoop)

Under the OpenCL NDRange model, a kernel function is invoked for a number of threads (work-itemss) that can cooperate and synchronize within a work-group. This model maps extremely well to GPUs, which have many Single Instruction, Multiple Data (SIMD) processors, but makes it difficult for kernel functions to express common work products. On FPGAs, where parallel kernels are implemented using pipelines, factoring out common work is key to improving performance. OpenCL allows thread and work-group sizes to be specified in three dimensions, denoted here as Z, Y, and X. The conversion of a NDRange kernel into a single work-items, transforms the kernel body into a series of loops over the respective n dimensions. Each loop executes the original kernel body for each thread. Thread ID references are remapped to the appropriate loop induction variable. Unfortunately, however, the number of dimensions, size, and count of work-groups are specified in host code and are inaccessible to device compilation. An example host invocation is shown in Figure 4.5.

Thus it is necessary to recover the number of dimensions, the starting indices of threads in each dimension, the number of threads in each dimension, and the number of threads per work-group in each dimension. To do so we created a host transformation that injects dummy functions that take as argument each value of interest. After this transformation, standard LLVM passes for inter-procedural constant propagation are applied. Calls to the dummy function are inspected, and constant arguments are transmitted to the device compiler. This technique can be easily extended to share arbitrary constants and ranges for device kernel parameters, allowing additional device code specialization. For generality, the kernel function signature is first modified to take as argument the work\_dim, global\_work\_offset, global\_work\_sizes and local\_work\_size values. Then, the results of the host NDRange invocation analysis are read, and used in place of the kernel arguments when available.

As long as a kernel contains no synchronization points, which can be verified by checking the kernel for calls to the OpenCL barrier() function, the NDRange execution can be emulated through a single loop nest. To emulate work-groups, the kernel body is wrapped in loops corresponding to any dimensions for which get\_group\_id() is accessed. Calls to get\_group\_id() are then replaced with accesses to the appropriate loop induction variables. Next, loops are inserted to emulate work-itemss within each work-group, replacing accesses to get\_local\_id() and get\_global\_id() with the appropriate expressions on the loop induction variables. Finally, accesses to the invocation dimensions are replaced. As an example, a Hello World kernel is shown in Figure 4.6. After applying the transformations above, the kernel appears as depicted in Figure 4.7. Several optimizations can be performed at this point. Single-iteration loops can be elided entirely, and dead code elimination can remove the computation of unnecessary values. By applying these optimizations, the single-work-items example can be simplified to Figure 4.8.

In NDRange kernels, work-itemss must halt execution at barrier points until all other work-itemss in the work-group reach the same point. This behavior can be preserved after NDRangeToLoop transformation by splitting work-items loop nests at each barrier point. Our prototype NDRangeToLoop transformation can only convert NDRange kernels with barriers in top-level control flow, outside of any conditional statements or loops. When such bar-

```

_kernel void hello_world

_kernel void hello_world

_kernel void hello_world

\begin{array}{c} 1 \\ 2 \\ 3 \\ 4 \end{array}

\begin{array}{r}

2 \\

3 \\

4 \\

5 \\

6 \\

7 \\

8 \\

9 \\

10 \\

\end{array}

(int tid) {

(int tid,

\frac{2}{3}

(int tid,

int offset_x, int offset_y,

int offset_x, int offset_y,

int offset_z,

int offset z.

int global_x, int global_y,

int global_x, int global_y,

6

7

8

9

int global_z,

6

7

8

9

int global_z,

int local_x, int local_y,

int local_z) {

int local_x, int local_y,

int local_z) {

int group_sz_x

10

10

(global_x-1) / local_x+1;

1\dot{1}

11

for (int c=0; c<group_sz_x; c++)</pre>

11

for (int c = 0; c < 2; c++) {

12

12

for (int f=0; f<local_x; f++) {

12

for (int f = 0; f < 32; f++) {

unsigned thread_id =

13

unsigned thread_id =

13

unsigned thread_id =

13

14

15

16

(c * 32) + f;

get_global_id(0);

14

(c*local_x + offset_x)+f;

14

if (thread_id == tid) {

printf("tid #%u\n", tid);

}

if (thread_id == tid) {

15

if (thread_id == tid) {

15

printf("tid #%u\n", tid);

16

16

printf("tid #%u\n", tid);

18

19

20 }

18

19

18

19

}

}

20 1

20 1

```

Figure 4.6: HelloWorld Ker-Figure 4.7: After NDRangeFigure 4.8: After Constant nel. From [2]. Propagation [2].

riers are encountered, the kernel is partitioned into unsynchronized sections, and each section is wrapped separately into work-items loop nests.

If values are calculated before and used after a barrier, they must be preserved across work-items loops. These values are identified by inspecting instruction operands, and then collecting operands calculated in a different partition than the user. Local arrays equal in size to the work-group are allocated, and each operand is saved into the array as it is calculated. Then, uses in other partitions are redirected to the allocated array.

After transforming the NDRange kernel to a single work-items kernel, it is necessary to transform the kernel invocation on the host. To invoke transformed device kernels appropriately, each clenqueueNDRangeKernel() invocation is replaced with the following routine:

- 1. Ensure that the kernel about to be executed is one which was transformed. If not, invoke with the original call to clEnqueueNDRangeKernel()

- 2. Pass the original dimensions and work-group sizes and counts as arguments through clSetKernelArg().

- 3. Invoke the kernel with clEnqueueTaskKernel() for single work-items execution.

Figure 4.4: Custom OpenCL Compilation Flow

The prototype implementation of the NDRange transformation described and evaluated in this work has some limitations. Its NDRange-ToLoop cannot handle barriers inside controlflow. Also, the workgroup size must be known at compile-time to enable the allocation of the array to allow uses across partitions.

## 4.3.2 Reduction-Dependence Elimination

The floating-point reductiondependence elimination transformation implements an idiom suggested by the Intel FPGA Best Practices Guide [31] as a technique to remove loopcarried dependencies by

inferring shift registers for loops that carry out floating-point reductions, as demonstrated by going from Figure 4.2 to Figure 4.3.

First, an analysis detects all reduction idioms that are safe to transform. All loops that do not contain other loops are scanned for reduction expressions. A reduction expression a store to a value where an operand of the stored value is obtained from a load from the same address. The pattern-matcher handles two cases: when the reduction value is accessed through a pointer with no

offset, and when the reduction value is a memory location specified via a base address and an indexing expression. The latter case requires the use of exactly the same indexing expression for both the store and the corresponding load. Once a reduction expression is found, the analysis must verify if it is safe and beneficial to apply the transformation. To do so, the analysis performs the following checks:

- The type of the reduction value must be either 32-bit or 64-bit floating-point.

- The reduction value must not be used elsewhere in the loop body other than in the reduction operation.

- If reduction is done on an array element, the indexing expression and the array base pointer must be loop invariant.

- The binary operations that constitute the reduction must be associative and commutative.

- If the loop trip count is known at compilation time and is less than the shift register size, the reduction should not be transformed.