# Optimization techniques for fine-grained communication in PGAS environments

Michail Alvanos

Submitted in in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Architecture

Universitat Politècnica de Catalunya October 2013 Barcelona, Spain

#### Department of Computer Architecture Universitat Politècnica de Catalunya

# Optimization techniques for fine-grained communication in PGAS environments

Author: Michail Alvanos

Supervisors: Xavier Martorell

Associate Professor

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

José Nelson Amaral

Professor

Department of Computing Science

$University\ of\ Alberta$

Montse Farreras

Professor Collaborator

Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

Barcelona, August 2013

#### Abstract

Partitioned Global Address Space (PGAS) languages promise to deliver improved programmer productivity and good performance in large-scale parallel machines. However, adequate performance for applications that rely on fine-grained communication without compromising their programmability is difficult to achieve. Manual or compiler assistance code optimization is required in order to avoid fine-grained accesses. The downsides to manually applying code transformations are the increased program complexity and hindrance of the programmer's productivity. On the other hand, compiler optimizations of fine-grained accesses require knowledge of physical data mapping and the use of parallel loop constructs.

This thesis presents optimizations for solving the three main challenges of the fine-grained communication: (i) low network communication efficiency; (ii) large number of runtime calls; and (iii) network hotspot creation for the non-uniform distribution of network communication. To solve these problems, the dissertation presents three candidate solutions. It presents first an inspector-executor transformation for improving the network efficiency through runtime aggregation. Second, it presents incremental optimizations to the inspector-executor loop transformation to automatically remove the runtime calls. Finally, the thesis presents a loop scheduling transformation for avoiding network hotspots and the over-subscription of nodes. In contrast to previous work that use static coalescing, prefetching, limited privatization, and caching, the solutions presented in this thesis focus cover all aspects of fine-grained communication, including reducing the number of calls generated by the compiler and minimizing the overhead of the inspector-executor optimization.

A performance evaluation that uses various microbenchmarks and benchmarks, and presenting scaling and absolute performance numbers of a Power 775 machine, indicates that applications with regular accesses can achieve up to 180% of the performance of hand-optimized versions. In contrast, the transformations yield from 1.12X up to 6.3X speedup in applications with irregular accesses. The loop scheduling shows performance gains between +3% and +25% for NAS FT and bucket-sort benchmarks, and up to 3.4X speedup for the microbenchmarks.

## Acknowledgments

When you set sail for Ithaca, wish for the road to be long, full of adventures, full of knowledge. – Ithaca, Constantine P. Cavafy

During the journey of the thesis, I have been fortunate to enjoy the advice, support, and friendship of a number of extraordinary people. I would like to thank each and every one of them. First of all, i would like to thank my supervisors Xavier Martorell, Montse Farreras, and José Nelson Amaral for their assistance and guidance during this work. They have offered me guidance and support in various ways. I started working with Xavier Martorell and Montse Farreras in the first stages of the thesis. Later Nelson offered some help with the compiler aspects of one paper and from that moment he stayed until the end. He acted as a catalyst during the process of the thesis.

I would like to thank many people from the IBM Toronto software lab and IBM T.J. Watson Research Center. First of all, i would like to thank Ettore Tiotto. Despite the time constraints and all the burden of managing the XL UPC compiler and runtime group, he was always available to help, not only for the administrative work, but also for technical level. His advices saved precious time and effort and provided guidance for the fast completion of the project. Furthermore, i would like to thank Nancy Wang for testing of the code and reporting bugs. Yaxun Liu for the setting environment and running the benchmarks in large scale. Gheorge Almasi, Ilie Gabriel Tanase, and Barnaby Dalton for their patience and support during the runtime developing. We had plenty and helpful discussions with Ilie Gabriel Tanase regarding the performance of the XL UPC compiler, especially in the last part of the thesis. I would like also to thank Patricia Clark and Debra A Domack for the access to Power 775 machines. Anny Ly for the interesting discussions about the performance of the Power 775 machines. Yaoqing Gao for reviewing the papers due to Canada Lab Publishing Process. I would like to thank the people working on the Center of Advanced Studies (CAS) that helped during my stay on IBM Toronto: Jimmy Lo, Debbie Kilbride, and Emillia Tung. I would like to extend my gratitude to all the people of the IBM Toronto Software laboratory and IBM T.J Watson Research Center that help me during the various stages of this

I would like also to thank the IBM CAS students and Canadian friends: Carolina Simoes Gomes, Maria Attarian, Marios Fokaefs, Bo Wu, Joan Guisado Gòmez, Thomas Reidemeister, Norha M. Villegas, Michalis Athanasopoulos, and Mary Christmas (Maria Tsimpoukelli). These people make my stay in IBM Canada easier by having a lot of fun. My friends in Barcelona Supercomputing Center that all surrounded these years: Ivan Tanasic, Javier Cabezas, Marc Jorda, Lluc Alvarez, Lluis Vilanova, Thomas Grass, Xavier Teruel, Javier Bueno,

and Leonidas Kosmidis. Special thanks to Thanos Makatos, Dagalaki Efsevia, Vicky Antoniadou, George Nikiforos, Kallia Chronaki, Nohelia Meza, and Angely Bahamón because they were there when needed them most! I would also like to thank all of my old friends for the encouragement: Matthaios Kavalakis, Yannis Klonatos, Nikiforos Manalis, Billy Vassilaras, John Aparadektos Manousakis, Christos Margiolas, Maria Zaharaki, and Maria Psaraki. After so many years and living in different parts of the world, we always find some time to speak to each other! Last but not least, I would like to thank my family for their support in many aspects.

This work is supported by the IBM Centers for Advanced Studies Fellowship contracts no. CAN10003-025 / CAN11001-11-24 / CAS2012-069 / CAS2013-12, by the Spanish Ministry of Science and Innovation through the grant CAN13001-779, and the Defense Advanced Research Projects Agency under its Agreement No. HR0011-07-9-0002. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the funding agencies.

Michail Alvanos Barcelona, 2013 Στην μνήμη της γιαγιάς μου Νικολέτας. Στην μνήμη του Ιωάννη Γιαννέζου. Στους γονείς μου Νικολαος και Χρυσοπηγή. Στον αδερφό μου Ιωάννη.

To the memory of my grandmother Nikoleta. To the memory of Ioannis Yiannezos. To my parents Nikolaos and Chrysopigi. To my brother John.

# Contents

| 1   | Introduction                                         | 1  |

|-----|------------------------------------------------------|----|

| 1.1 | Objective of the thesis                              | 2  |

|     | 1.1.1 Dynamic Data Coalescing                        | 3  |

|     | 1.1.2 Reducing the overhead of inspector-loops       | 4  |

|     | 1.1.3 Improving the all-to-all communication pattern | 4  |

| 1.2 | Contributions                                        | 5  |

|     | Outline                                              | 5  |

| 2   | Background                                           | 7  |

| 2.1 | Partitioned Global Address Space Languages           | 7  |

|     | Unified Parallel C                                   | 7  |

|     | Overheads of fine-grained accesses                   | 11 |

| 2.4 | The IBM UPC Compiler and Runtime System              | 14 |

|     | 2.4.1 XL UPC Compiler Framework                      | 14 |

|     | 2.4.2 Runtime                                        | 18 |

| 3   | Experimental Setup                                   | 21 |

|     | The hardware environment                             | 21 |

|     | Available Benchmarks                                 | 25 |

| J   | 3.2.1 Micro Benchmarks                               | 25 |

|     | 3.2.2 Applications                                   | 26 |

| 4   | Dynamic Data Aggregation                             | 33 |

|     | Approaches and solutions                             | 33 |

|     | 4.1.1 Inspector-executor strategy                    | 34 |

|     | 4.1.2 Double buffering                               | 35 |

|     | 4.1.3 Loop versioning                                | 36 |

| 4.2 | Implementation                                       | 36 |

|     | 4.2.1 Transformation algorithm                       | 36 |

|     | 4.2.2 Runtime support                                | 40 |

|     | 4.2.3 Resolving Data Dependencies                    | 42 |

| 43  | Experimental Results                                 | 43 |

| 1.0 | 4 3 1 Benchmark versions                             | 44 |

|     | 4.3.2 Microbencmarks Performance                                        | 45                   |

|-----|-------------------------------------------------------------------------|----------------------|

|     | 4.3.3 Applications Performance                                          | 49                   |

|     | 4.3.4 Where does the time go?                                           | 53                   |

|     | 4.3.5 Cost of the optimization                                          | 53                   |

|     | Chapter Summary and Discussion                                          | 54                   |

| 5   | Reducing the Runtime Calls                                              | 57                   |

|     | Inspector-executor Optimizations                                        | 57                   |

|     | 5.1.1 Constant Stride Linear Memory Descriptors                         | 58                   |

|     | 5.1.2 CSLMADs in dynamic environments                                   | 59                   |

|     | 5.1.3 Usage of vectors to collect shared indexes                        | 60                   |

|     | 5.1.4 Combining Dynamic with Static Coalescing                          | 60                   |

|     | 5.1.5 Inline checks                                                     | 63                   |

|     | 5.1.6 Optimization Integration                                          | 64                   |

|     | Shared-reference-aware loop-invariant code motion and privatization for | 01                   |

|     | PGAS languages                                                          | 65                   |

|     | Experimental Results                                                    | 66                   |

|     | 5.3.1 Methodology                                                       | 66                   |

|     | 5.3.2 Microbenchmark Performance                                        | 68                   |

|     |                                                                         | 69                   |

|     | 5.3.3 UPC Single-Threaded Slowdown                                      | 70                   |

|     | 5.3.4 Applications Performance                                          | 70                   |

|     | 5.3.5 Parameter exploration                                             | 76                   |

|     | 5.3.6 Overhead Analysis                                                 |                      |

|     | 5.3.7 Compilation Time and Code Length                                  | 76<br>70             |

| 5.4 | Chapter Summary and Discussion                                          | 78                   |

| 6   | Loop Scheduling                                                         | 81                   |

| 6.1 | Loop scheduling                                                         | 82                   |

|     | 6.1.1 Approaches                                                        | 82                   |

|     | 6.1.2 Compiler-assisted loop transformation                             | 84                   |

| 6.2 | Experimental results                                                    | 85                   |

|     | 6.2.1 Methodology                                                       | 86                   |

|     | 6.2.2 Limit study                                                       | 87                   |

|     | 6.2.3 Compiler-assisted loop transformation                             | 88                   |

|     | Chapter Summary and Discussion                                          | 90                   |

| 7   | Related Work                                                            | 93                   |

|     | Prefetching                                                             | 93                   |

|     | Inspector-executor approaches                                           | 93                   |

|     | Compile-time Optimizations                                              | 93<br>94             |

|     | 7.3.1 Code simplification                                               | 9 <del>4</del><br>95 |

|     | 7.3.2 Shared-Pointer Privatization                                      | 95<br>95             |

|     |                                                                         |                      |

|     | 7.3.3 Shared Object Coalescing                                          | 96                   |

|     | 7.3.4 Overlapping of communication and computation                      | 97                   |

| 7.4 Runtime optimizations              | 98         |

|----------------------------------------|------------|

| 7.4.1 Software caching                 | 98         |

| 7.4.2 Hybrid environments              | 99         |

| 7.5 Loop Scheduling                    | 99         |

| 7.6 Language Extensions                | 100        |

| 7.7 Application specific optimizations | 100        |

| 7.8 Array Accesses Analysis            | 101        |

| 8 Conclusions and Future Work          | 103        |

| 8.1 Publications                       | 104        |

| 8.2 Productization                     | 106        |

| 8.3 Future Work                        | 106        |

| 8.4 Survival of the UPC language       | 107        |

| Appendix                               | 123        |

| A Terminology                          | <b>123</b> |

# List of Figures

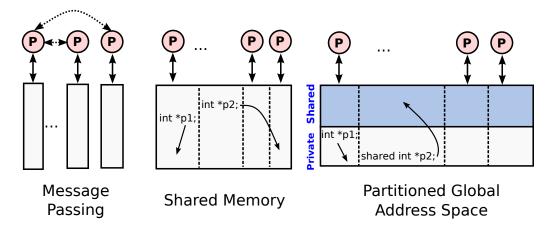

| 2.1  | Comparison of parallel programming models                             | 8  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Comparison of different data blocking possibilities                   | 10 |

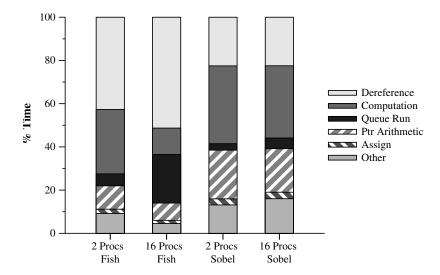

| 2.3  | Normalized execution time breakdown of gravitational fish and sobel   |    |

|      | benchmarks using 2 and 16 processes                                   | 11 |

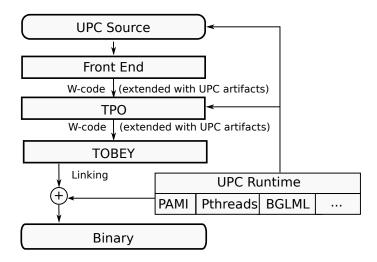

| 2.4  | XL UPC compiler framework                                             | 14 |

| 2.5  | Example of privatization optimization                                 | 16 |

| 2.6  | Example using the array idiom recognition                             | 17 |

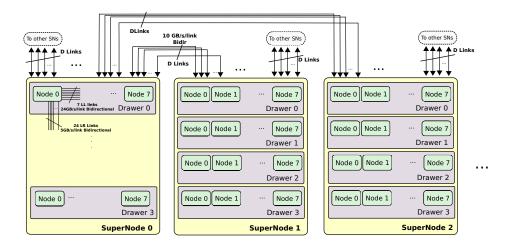

| 3.1  | Architecture of the machine                                           | 22 |

| 3.2  | UPC benchmark ping-pong for one (left) and two (right) supernodes.    | 23 |

| 3.3  | Unidirectional point-to-point bandwidth between two different cores.  | 24 |

| 3.4  | WaTor benchmark: architecture (left), smell update (middle), and      |    |

|      | force calculation (right)                                             | 28 |

| 4.1  | Final version after the loop versioning                               | 38 |

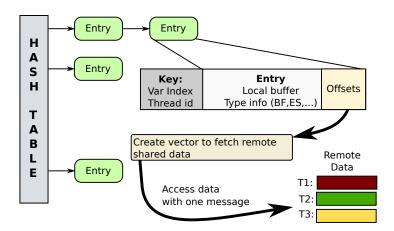

| 4.2  | Runtime internal implementation                                       | 41 |

| 4.3  | The runtime resolves dependencies with the help of the compiler       | 43 |

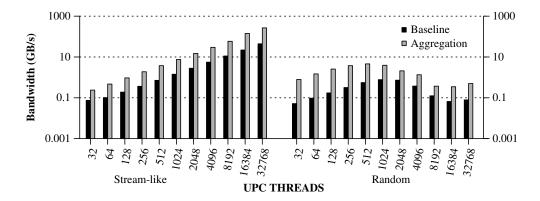

| 4.4  | Performance in GB/s for the microbenchmark reading four fields        |    |

|      | from the same data structure in streaming and random fashion          | 45 |

| 4.5  | Achieved speedup for the two microbenchmark variations                | 45 |

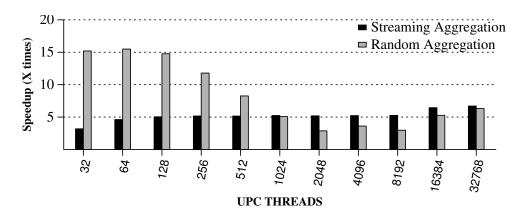

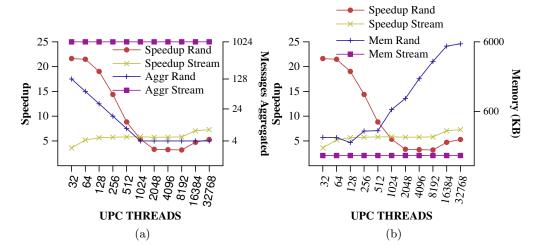

| 4.6  | Achieved speedup for the two microbenchmark variations compared       |    |

|      | with the number of messages aggregated (left), and speedup com-       |    |

|      | pared with the memory consumption of the runtime (right)              | 47 |

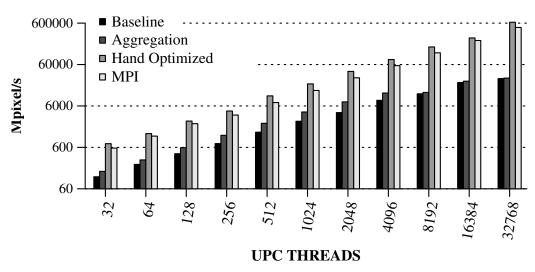

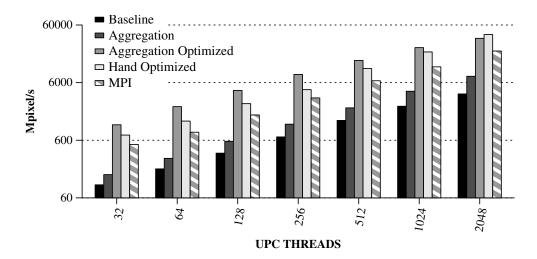

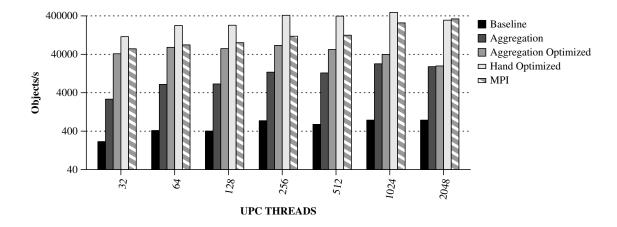

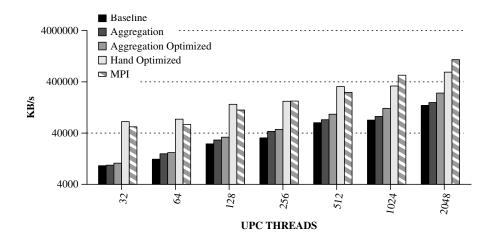

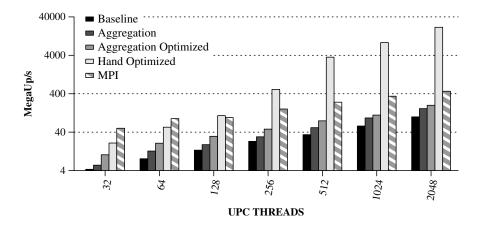

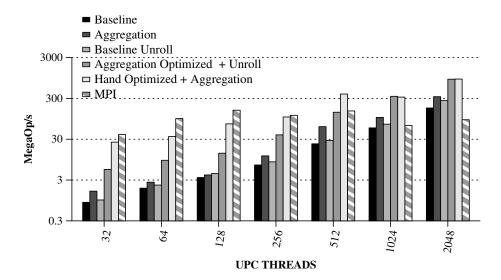

| 4.7  | Performance numbers for the sobel benchmark using different versions. | 49 |

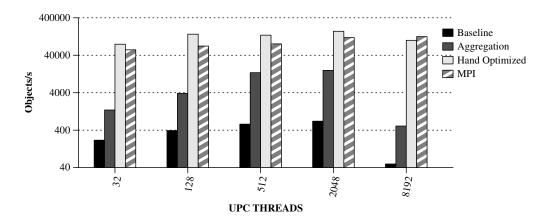

| 4.8  | Performance numbers for the gravitational fish benchmark using        | 50 |

| 4.0  | different versions.                                                   | 50 |

| 4.9  | Performance numbers for the WaTor benchmark using different versions. | 51 |

| 4.10 |                                                                       | 52 |

|      | Performance numbers for the Guppie benchmark                          |    |

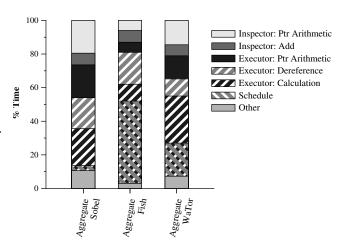

|      | Performance numbers for the MCop benchmark                            | 52 |

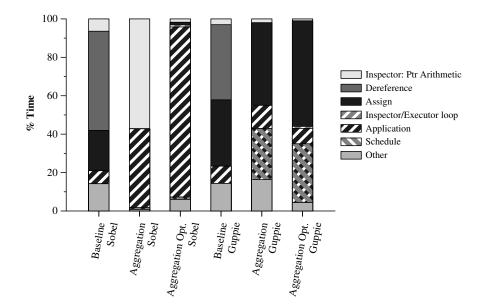

| 4.12 | Normalized execution time breakdown of the benchmarks using 128       | 53 |

|      | UPC threads                                                           | 99 |

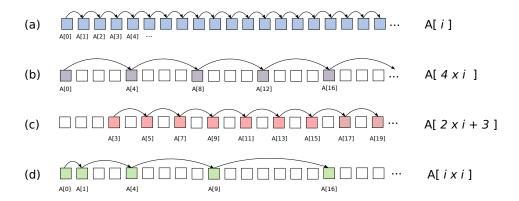

| 5.1  | Examples of array accesses that Linear Memory Access Descriptors can represent. The LMADs can represent (a), (b), and (c) but not | <b>F</b> 0 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.2  | (d) The shared address translation problem. The program access the                                                                | 58         |

| J.∠  | data range from 5 up to 19                                                                                                        | 59         |

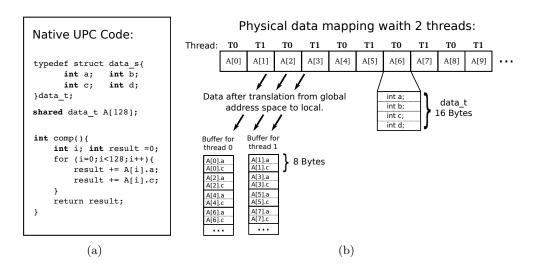

| 5.3  | Example of Static data coalescing: native UPC source code (left),                                                                 | 00         |

| 0.0  | and physical data mapping (right)                                                                                                 | 62         |

| 5.4  | Final code modification and a high level implementation of the run-                                                               | 0 <b>2</b> |

| J. 1 | time                                                                                                                              | 63         |

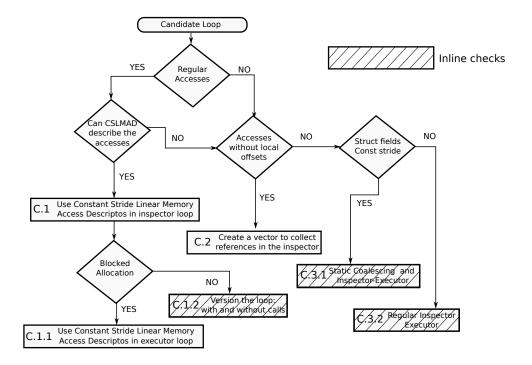

| 5.5  | Improvements for the for the inspector-executor compiler transfor-                                                                |            |

|      | mation.                                                                                                                           | 64         |

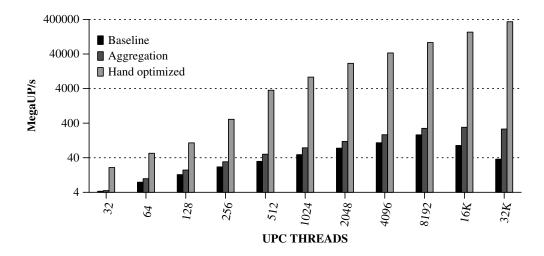

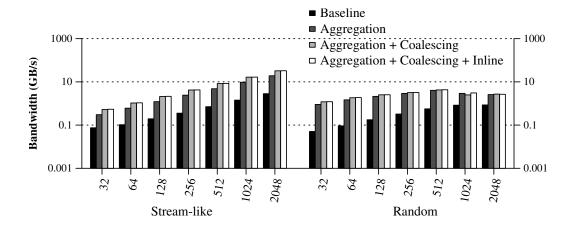

| 5.6  | Performance in GB/s for the microbenchmark reading four fields                                                                    |            |

|      | from the same data structure reading four fields                                                                                  | 68         |

| 5.7  | Performance numbers for the Sobel benchmark for different versions.                                                               | 71         |

| 5.8  | Performance numbers for the Fish benchmark for different versions.                                                                | 71         |

| 5.9  | Performance numbers for the WaTor benchmark for different ver-                                                                    |            |

|      | sions                                                                                                                             | 72         |

| 5.10 | Performance numbers for the Guppie benchmark for different ver-                                                                   |            |

|      | sions                                                                                                                             | 73         |

|      | Performance numbers for MCop benchmark for different versions.                                                                    | 74         |

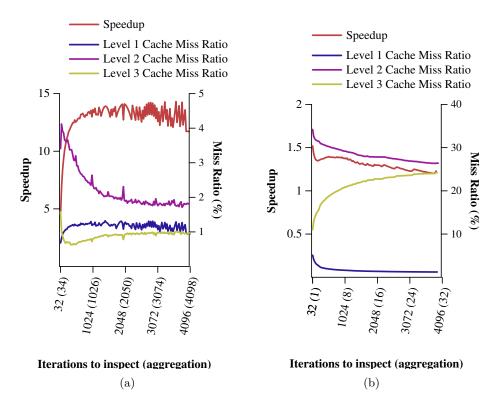

| 5.12 | Speedup and cache misses for Sobel (a) and Guppie (b) using dif-                                                                  |            |

|      | ferent number of iterations to inspect and aggregation levels                                                                     | 75         |

| 5.13 | Normalized execution time breakdown of the benchmarks using 32                                                                    |            |

|      | UPC threads                                                                                                                       | 77         |

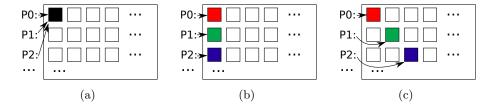

| 6.1  | Different schemes of accessing a shared array. The shared object is                                                               |            |

| 0.1  | allocating in blocked form. Each row represents data residing in one                                                              |            |

|      | UPC thread and each box is an array element. The different access                                                                 |            |

|      | types are: (a) baseline: all UPC threads access the same data; (b)                                                                |            |

|      | 'Skewed': each UPC thread access elements from a different UPC                                                                    |            |

|      | thread; (c) 'Skewed plus': each UPC thread access elements from a                                                                 |            |

|      | different thread and from a different point inside the block                                                                      | 84         |

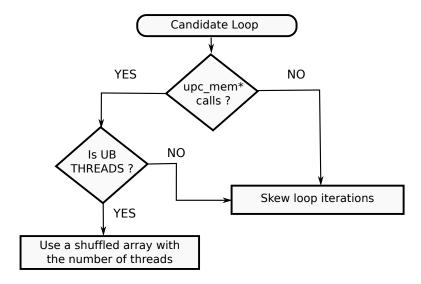

| 6.2  | Automatic compiler loop scheduling                                                                                                | 86         |

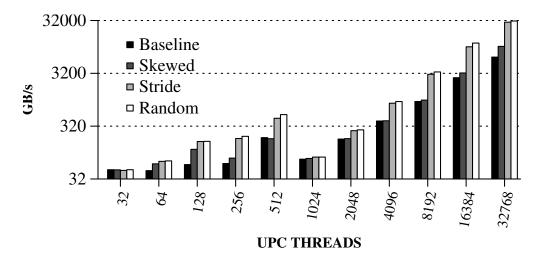

| 6.3  | Effect of loop scheduling policies on performance for upc_memput.                                                                 | 87         |

| 6.4  | Effect of loop scheduling policies on performance for fine-grained                                                                |            |

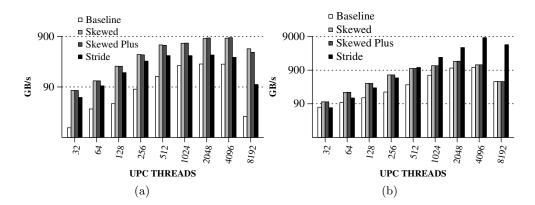

|      | get (b) and fine-grained put (c)                                                                                                  | 88         |

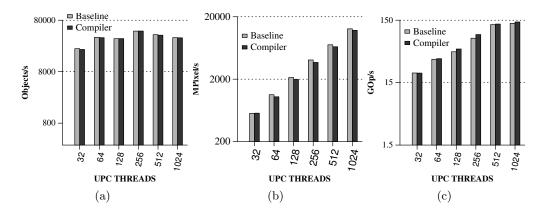

| 6.5  | Comparison of compiler-transformed and hand-optimized code: upc_n                                                                 | _          |

|      | (a), fine-grained get (b), and fine-grained put (c)                                                                               | 89         |

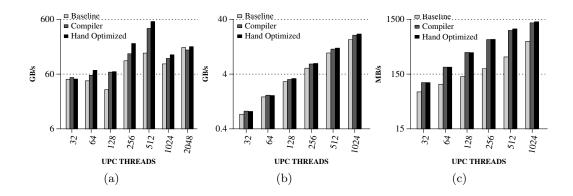

| 6.6  | Comparison of baseline and compiler-transformed code for fish (a),                                                                | 0.0        |

| c =  | Sobel (b), and NAS FT (c)                                                                                                         | 90         |

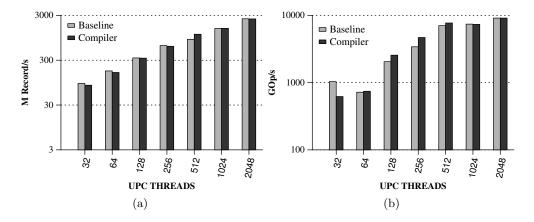

| 6.7  | Comparison of baseline and compiler-transformed code for bucket-                                                                  | 00         |

|      | sort (a) and bucket-sort with only the communication pattern (b).                                                                 | 90         |

| A 1  | Example of common subexpression elimination                                                                                       | 124        |

| A.2 | Example of constant propagation optimization | 125 |

|-----|----------------------------------------------|-----|

| A.3 | Example of loop blocking transformation      | 127 |

# List of Tables

| 3.1 | Theoretical peak uniform all-to-all bandwidth versus measured bandwidth for different machine configurations                                                                                              | 24 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Overview of micro-benchmarks                                                                                                                                                                              | 31 |

| 3.3 | Overview of available benchmarks. We provide the source code line number for reference                                                                                                                    | 31 |

| 4.1 | Percentage of traffic that uses remote and local links                                                                                                                                                    | 49 |

| 4.2 | Object file increase in bytes. We consider only the transformed file.                                                                                                                                     | 54 |

| 5.1 | Benchmarks compared with the serial C non-instrumented version                                                                                                                                            |    |

|     | and UPC version in execution time, measured in seconds                                                                                                                                                    | 69 |

| 5.2 | Benchmarks and different cost metrics. Object file sizes are in bytes and for the object files only.                                                                                                      | 78 |

| 6.1 | Local cache miss ratio using 256 Cores for Sobel benchmark using 256 UPC threads. Results are the average from each of 256 cores. Local miss ratio is calculated by diving misses in this cache the total |    |

|     | number of memory accesses to this level of cache.                                                                                                                                                         | 89 |

| 7.1 | Example using the pointer arithmetic optimization                                                                                                                                                         | 96 |

| 7.2 | Example using the coalescing optimization                                                                                                                                                                 | 96 |

| 7.3 | Example using the splitting optimization                                                                                                                                                                  | 97 |

#### Acronyms

**API** Application Programming Interface

**BF** Blocking Factor

CPU Central Processing Unit

CSLMAD Constant-Stride Linear Memory Access Descriptor

**DSM** Distributed Memory System

**FFT** Fast Fourier Transformation

GAS Global Address Space

**GPU** Graphics Processing Unit

LMAD Linear Memory Access Descriptor

MPI Message Passing Interface

**PF** Prefetch Factor

**PGAS** Partitioned Global Address Space Languages

SVD Shared Variable Directory

**TPO** Toronto Portable Optimizer

**UPC** Unified Parallel C

### Chapter 1

## Introduction

Next-generation architectures and large-scale parallel machines are increasing in size and in complexity. In this context, programming productivity is becoming crucial for software developers. Parallel languages and programming models need to provide simple means for developing applications that can run on parallel systems without sacrificing performance. New programming models provide attractive alternative ways of programming complex and parallel architectures. The programming model should provide a transparent method for effectively moving data without any efficiency loss relative to memory management.

The "automatic" memory management is becoming increasingly important for the compiler developer. The memory management must be transparent to the programmer, in a similar manner as the virtual memory in modern computers. High performance machines with attractive performance/price ratio are not enough to attract talented programmers into the High Performance Computing (HPC) due to complex programming. The productivity gap between distributed memory and shared memory machines is increasing especially with the standardization of the OpenMP [1] programming model.

A popular programming model for distributed systems is the Distributed Shared Memory systems (DSMs) [2, 3, 4, 5, 6]. Distributed Shared Memory (DSM) systems refer to a wide class of software and hardware implementations, in which each node of a cluster has access to shared memory in addition to each node's non-shared private memory. However, most of the DSM systems rely on the page fault mechanism with page prefetching and often have poor performance on fine-grained communication [7]. Partitioned Global Address Space (PGAS) [8, 9, 10, 11, 12, 13, 14, 15] languages introduce some complexity through the partitioning of data, due to low performance of the Global Address Space languages and software distributed shared memory systems. PGAS languages extend existing languages or create new ones with constructs to express parallelism and data distribution.

Partitioned Global Address Space programming languages provide a uniform programming model for local, shared and distributed memory hardware. The programmer sees a single coherent shared address space, where variables may be directly read and written by any thread, but each variable is physically associated with a single thread. These languages provide a simple, shared-memory-like programming model, where the address space is partitioned and the programmer has control over the data layout. They boost programmer productivity by using shared variables for inter-process communication instead of message passing [16, 17, 18].

#### 1.1 Objective of the thesis

The key insight that motivates PGAS languages is that accessing data using individual reads and writes to the shared space, just as any programmer would do in a serial application increases programmer productivity. In a distributed environment, however, this coding style translates into fine-grained communication, which has poor efficiency and hinders performance of PGAS applications. The low communication efficiency of fine-grained data accesses has been identified by many researchers [19, 20] as one of the main bottlenecks of PGAS languages.

Regardless of all research community efforts, the de facto programming model for distributed memory architectures is still the Message Passing Interface (MPI) [21]. One reason is that PGAS programs deliver scalable performance only when they are carefully tuned. Often, after initial coding, the programmer tunes the source code to produce a more scalable version. However, the reality is that, at the end of these modifications, the PGAS code resembles very much his MPI equivalent, often nullifying the ease-of-coding advantage of these languages. In PGAS languages, the programmer accesses the data using individual reads and writes to the shared space. However, in a distributed environment this coding style translates into fine-grained communication, which has poor efficiency and hinders performance of PGAS applications [22, 20]. Due to the poor performance of fine-grained accesses, PGAS programmers optimize their applications by using large data transfers, whenever possible.

This dissertation tries to answer the following question: Can applications written in the UPC programming model provide comparable performance with the hand-tuned MPI versions? The objective of this thesis is to improve performance of applications that use fine-grained communication, without hindering its programmability. The optimizations achieve comparable performance to the equivalent manual optimized versions. The thesis presents compiler and runtime optimizations for solving the three major problems of the fine-grained communications: (i) low efficiency of network communication; (ii) large number of runtime calls; and (iii) network hotspot creation for the non-uniform distribution of network communication, especially in all-to-all patterns. The work was carried out using the Unified Parallel C (UPC) language, although it can be applied to other PGAS languages as well.

#### 1.1.1 Dynamic Data Coalescing

The first part of the thesis provides solutions to the problem of low network efficiency created by fine-grained communication. The research community has proposed various techniques to decrease the performance penalty of fine-grained communication. Previous approaches to optimize the inter-node communication include the use of inspector-executor transformation [23, 24, 25, 26, 27, 28], static coalescing [22, 29, 30, 31], limited privatization [32, 33], and software cache [34, 35]. However, the existing solutions have two important limitations: (i) they require knowledge of physical data mapping at compilation time or the usage of a worksharing construct; (ii) they incur high overheads at runtime.

The programmer must specify the number of threads, the number of processing nodes, and the data distribution at compile time in order the compiler to have knowledge of physical data mapping at compile time (i). Also, the programmer must use worksharing constructs ( $upc_-forall$  in UPC) to help the compiler to optimize the accesses. Nevertheless, applications do not make extensive use of the worksharing construct in practice. Thus, a substantial number of shared accesses inside serial loops (for, while ...) are not optimized. In the second case (ii), the inspector-loop optimizations and cache systems usually produce high overheads that burden the application performance.

The first part of the thesis presents a compiler optimization with the proper runtime support to tolerate the latency of fine-grained accesses, through prefetching and coalescing techniques [36]. The optimization uses loop transformations and runtime support, to increase the communication efficiency and tolerate network latencies. The transformation uses the inspector-executor approach [24, 23, 37, 26] to discover the affinity between accesses and data allocation in the absence of explicit compile time affinity information, and thus to enable the runtime to coalesce fine-grained accesses.

The aggregated network communication has three advantages. (i) It amortizes the per-message overhead at the end-points over the large amount of data being sent. (ii) It amortizes the per-packet routing and header information. (iii) Large messages require only a single acknowledgement rather than one per message, which contributes to reduction of traffic, end-point overhead, and possible network contention.

However, this approach has two drawbacks. First, the inspector-executor transformation inserts additional overhead for analyzing and aggregating at runtime the shared data. To increase the efficiency of this optimization, the system uses double buffering techniques to amortize the overhead. The second source of overhead is the large number of runtime calls. The inspector-executor transformation injects more runtime calls for collecting and inspecting elements. Thus, the number of runtime calls is doubled. To solve this problem, the thesis proposes a number of compiler optimizations for removing the calls as we discuss in the following section.

#### 1.1.2 Reducing the overhead of inspector-loops

The inspector-executor transformation increases the network efficiency using large messages over the network interconnect. However, the transformation has a big disadvantage. The optimization increases the instrumentation overhead due to additional runtime calls in the inspector loop. The second part of the thesis, proposes different approaches to reduce the number of runtime calls. The thesis presents a set of compiler optimizations [38] to increase the efficiency of UPC language by removing runtime calls and addressing some of the weaknesses found in traditional compiler optimizations in loops. The techniques include inspector-executor improvements to decrease the overhead and a lightweight code invariant loop motion.

The first technique employed involves the usage of Constant Stride Linear Memory Address Descriptors (CSLMADs) [39], a restrictive form of Linear Memory Descriptors [40, 41]. CSLMADs constitute an efficient way to capture accurate array access information. Thus, the compiler can effectively remove the calls from the inspector and executor loops when the access pattern is regular. Furthermore, the compiler uses a temporary vector to collect the shared indexes in the inspector loops to improve performance on benchmarks with irregular access patterns.

The last part of this section presents a lightweight loop code motion. Loop-invariant code motion is a traditional compiler optimization which performs this movement automatically. The compiler automatically moves outside of the loop main body statements and expressions that don't affect the semantics of the program. However, shared scalar and pointers can make the analysis hard, leaving some shared accesses inside the body of the loop. The algorithm uses the reaching definitions analysis through the Static Single Assignment (SSA) [42] representation to detect and move the statements that use shared variables before the loop.

#### 1.1.3 Improving the all-to-all communication pattern

The last part of the thesis presents optimizations for improving the network communication and avoiding the creation of hotspots. In order to effectively avoid congestion the programmer or the runtime must spread non-uniform traffic evenly over the different links. Moreover, an important number of UPC applications that require all-to-all communication can create hotspots during the communication without the awareness of the programmer. This pattern shows up in a large number of scientific applications including FFT, Sort, and Graph 500. The UPC programs can suffer from shared access conflicts on the same node and network link congestion.

This section first explores the possible approaches to distributing the accesses through the network by manually modifying the source code. Next, the thesis presents a loop transformation technique that improves the performance of the all-to-all communication without the programmer's interference. The transformation "skews" or randomly distributes the traffic using all the UPC threads to reduce the

possibility of hotspot creation on the interconnection network and overwhelming of the nodes.

#### 1.2 Contributions

This dissertation presents how new programming models provide comparable performance with the message passing models, when using fine-grained communication. The thesis makes the following contributions:

- It presents coalescing and prefetching techniques that use loop transformations and runtime support to increase communication efficiency and tolerate the network latencies [43, 36, 38]. It demonstrates that dynamic analysis and coalescing at runtime can significantly improve the performance of fine-grained accesses inside loops, without having to know the physical data mapping or use the *upc\_forall* parallel structure.

- It proposes a number of optimizations to decrease the impact of library calls that fine-grained communication produces [38]. The optimizations include an analysis based on Constant-Stride Linear Memory Descriptors (CSLMADs), insertion of inline checks for local data, and a new shared-reference-aware loop-invariant code motion. This latter, is designed specifically for PGAS languages, to deliver improved performance for benchmarks that rely on fine-grained communication. This new approach to the compilation of PGAS applications results in programs containing fine-grained access benchmarks having comparable performance to that of coarse-grained benchmarks.

- It presents a compiler loop transformation that automatically schedules the loop iterations to increase the applications performance by decreasing the potential contention of the network [44, 45]. The evaluation shows that a compilers can provide comparable performance to the manual modified loop.

#### 1.3 Outline

The remainder of this thesis is organized as follows. Chapter 2 introduces the Unified Parallel C programming language and the IBM XL UPC compiler framework. Chapter 3 presents the hardware environment and the benchmarks used for the evaluation. Chapter 4 demonstrates the inspector-executor transformation and runtime dynamic aggregation of shared-objects. Chapter 5 presents compiler transformations to reduce the overhead of the automatically compiler created calls. Chapter 6 presents approaches and compiler transformations to improve the performance of network using loop scheduling. The related work is reviewed in Chapter 7. Chapter 8 draws conclusions based on the findings, and discusses future research plans.

## Chapter 2

## Background

#### 2.1 Partitioned Global Address Space Languages

Partitioned Global Address Space Languages (PGAS) programming languages provide a uniform programming model for local, shared and distributed memory hardware. The programmer sees a single coherent shared address space, where variables may be directly read and written by any thread, but each variable is physically associated with a single thread. PGAS languages, such as Unified Parallel C [9], Co-Array Fortran [10], Fortress [11], Chapel [12], X10 [13], Global Arrays [46], and Titanium [14], extend existing languages with constructs to express parallelism and data distribution.

The message passing models, such as MPI [21], use library calls for explicit communication between processes. On the other hand, in PGAS languages, the programmer can access each variable between processes without knowing if the access is remote or local. Figure 2.1 presents the differences between the programming models. Example implementations of shared memory programming model are the OpenMP [1] and Pthreads [47]. The downside of this approach is that the programmer is not always aware of the locality of data and can use remote accesses that lead to performance degradation. Other popular alternative shared memory programming models are for the Software Distributed Memory Systems (DSMs)[2, 3], such as Nanos DSM [4], ThreadMarks [5] and ParaADE [6]. Similarly to the PGAS, the programmer sees a global address space and the runtime is responsible for the communication.

#### 2.2 Unified Parallel C

The Unified Parallel C (UPC) [9] is an example of PGAS programming model as an extension of the C programming language [48] designed for high performance computing on large-scale parallel machines. UPC uses a Single Program Multiple Data (SPMD) model of computation in which the amount of parallelism is fixed at program startup time, typically with a single thread of execution per processor.

Figure 2.1: Comparison of parallel programming models

In all cases, the compiler translates the shared remote access to runtime calls for fetching and storing the data. The result is portable high-performance compilers that run on a large variety of shared and distributed memory multiprocessors.

In order to better understand the concept of UPC programming model, this section explains the basic C language extensions. In UPC, there are two new keywords, the keyword 'THREADS' that describes the total number of threads and the keyword 'MYTHREAD' that describes the thread identifier starting from 0. The language defines two different types of variables, the *shared* and the *private*. The shared variables must be explicitly declared by using the keyword shared or they are considered private. The shared variables are used for communication between threads because they are visible from any thread. The private variables can only be accessed by a single thread. To access shared variables, the programmer must specify the keyword shared to the pointer declaration.

```

int OUT[N][N];

2

int IN[N][N];

3

4

void stencil_kernel(){

5

int i,j;

for(i=1; i<N-1; i++ ){</pre>

6

7

for(j=1; j<N-1; j++){</pre>

OUT[i][j] = 0.25f * (IN[i-1][j] + IN[i+1][j] +

8

9

IN[i][j-1] + IN[i][j+1]);

10

11

}

12

}

```

Listing 2.1: Serial version of a stencil kernel.

Furthermore, in UPC there is a new type of for loop, the upc\_forall loop, in which the iterations are executed in parallel, according to the language semantics. Each thread executes a fraction of iterations concurrently with other threads. At

the header of the loop, there is an additional expression, called affinity expression. The affinity expression specifies which executions of the loop will be performed by a thread.

Listing 2.1 presents a serial version of a stencil benchmark. A straightforward UPC parallel version is shown in Listing 2.2. Arrays IN and OUT are declared as shared (lines 1-2), and their elements will be distributed cyclically among the threads. The construct upc\_forall distributes loop iterations among the UPC threads. The affinity expression (&OUT[i]) in the upc\_forall construct specifies that the owner thread of the specified element &OUT[i] will execute the *i*th loop iteration.

```

shared int OUT[N][N];

shared int IN[N][N];

3

4

void stencil_kernel(){

5

int i,j;

upc_forall(i=1; i<N-1; i++; &OUT[i] ){</pre>

6

7

for(j=1; j<N-1; j++ ){</pre>

8

OUT[i][j] = 0.25f * (IN[i-1][j] + IN[i+1][j] +

9

IN[i][j-1] + IN[i][j+1]);

10

11

}

12

}

```

Listing 2.2: Parallel version of a stencil kernel.

In this example access locality to array OUT is developed through the use of the affinity expression. Each runtime call may imply communication of one element of the array, leading to fine-grained communication which leads to poor performance. Communication traffic in this case is  $O(N \times N)$  elements.

```

#define B N*(N/THREADS)

shared [B] int OUT[N][N];

3

shared [B] int IN[N][N];

4

5

void stencil_kernel(){

6

int i,j;

upc_forall(i=1; i<N-1; i++; &OUT[i] ){</pre>

7

8

for(j=1; j<N-1; j++){</pre>

9

OUT[i][j] = 0.25f * (IN[i-1][j] + IN[i+1][j] +

10

IN[i][j-1] + IN[i][j+1]);

11

12

}

13

}

```

Listing 2.3: Blocked parallel version of a stencil kernel.

A better distribution of the shared data can be achieved through the use of layout modifiers. Listing 2.3 shows a distribution by rows, where each thread owns n consecutive rows. Where n = N/THREADS as specified by the [B]

| Threads Data                                                             |                                               | Threads Data       |                                                     | Threads                | Data                                |

|--------------------------------------------------------------------------|-----------------------------------------------|--------------------|-----------------------------------------------------|------------------------|-------------------------------------|

| 0                                                                        | $\begin{pmatrix} 0 & 1 & 2 & 3 \end{pmatrix}$ | 0                  | 0 4 8 12                                            | 0                      | 0 1 2 3 4                           |

| 1                                                                        | $\begin{pmatrix} 4 & 5 & 6 & 7 \end{pmatrix}$ | 1                  | 1 5 9 13                                            | 1                      |                                     |

| 2                                                                        | 8 9 10 11                                     | 2                  | 2 6 10 14                                           | 2                      |                                     |

| 3                                                                        | 12 13 14 15                                   | 3                  | 3 7 11 15                                           | 3                      |                                     |

| <pre>shared [16/4] int array[16]; or<br/>shared [*] int array[16];</pre> |                                               | shared [<br>shared | <pre>1 ] int array[16]; or<br/>int array[16];</pre> | shared [0<br>shared [] | )] int array[16]; or int array[16]; |

Figure 2.2: Comparison of different data blocking possibilities.

blocking factor. The Blocking Factor (BF) is layout qualifier that dictates the number of successive elements placed on the same UPC thread. This feature gives the option to the programmer to select the data partitioning. The selection of proper blocking scheme can significantly affect the performance of the application. Programmers use two common blocking schemes: the 'blocked' or the 'cycled'. Figure 2.2 illustrates the different blocking schemes with the array declarations. Note that the programmer has also the possibility to allocate shared objects or arrays with affinity to only one UPC thread (Figure 2.2 right).

```

typedef struct {int r[N];} Row;

2 shared [*] Row IN[N+2*THREADS];

3

shared [*] Row OUT[N+2*THREADS];

void stencil_kernel(){

6

int i,j;

7

int lower, upper;

8

int rowspp;

9

rowspp = (N+2*THREADS)/THREADS;

10

lower = MYTHREAD*rowspp;

11

upper = (MYTHREAD+1)*rowspp -1;

12

/* exchange shadows - (code incomplete, no bounds check) */

/* shadow for lower boundary */

13

14

upc_memget(&IN[lower], &IN[lower-2], sizeof(Row));

/* shadow for upper boundary */

15

16

upc_memget(&IN[upper], &IN[upper+2], sizeof(Row));

17

for(i=lower; i<upper; i++){</pre>

18

for(j=1; j<N-1; j++ ){</pre>

19

OUT[i].r[j] = 0.25f * (IN[i-1].r[j] + IN[i+1].r[j] +

20

IN[i].r[j-1] + IN[i].r[j+1]);

21

}

22

}

23 }

```

Listing 2.4: Stencil optimized parallel version.

In this example, the non-local read memory accesses are reduced to  $O(2 \times N \times THREADS)$  because only computation of positions in the boundary of each

Figure 2.3: Normalized execution time breakdown of gravitational *fish* and *sobel* benchmarks using 2 and 16 processes.

thread data access remote data. However, one access per element is still performed, leading to fine-grained communication.

To avoid fine-grained communication the UPC language provides data movement primitives: upc\_memget, upc\_memput, and upc\_memcpy. In listing 2.4, the lower and upper boundary rows of the IN array on each thread are copied into a shadow row which is local to that thread. The number of accesses decreases to  $O(2 \times THREADS)$ , each access bringing a row of size N. This code has better performance although, the programmability has been hindered. This contradicts the philosophy of PGAS languages: ease of programming and productivity.

### 2.3 Overheads of fine-grained accesses

When the physical data mapping is unknown at compiler time, the compiler does not apply most of the UPC specific optimizations. Two problems arise from these codes with fine-grained accesses to shared data: (i) low communication efficiency because of the use of small messages, and (ii) high overhead due to the large number of runtime calls created.

Figure 2.3 presents the execution time breakdowns of two different benchmarks: fish [49] and Sobel [50]. It shows that little time is spent on the actual computation: 30% in fish and 35% in Sobel with 2 UPC threads. Several sources of overhead are identified: (i) time spent in accessing shared data (dereference phase) shows the impact of the communication latency for fine-grained accesses where communication is necessary for each dereference call; (ii) Shared pointer arithmetic (Ptr Arithmetic) also has an impact since shared pointers contain more

information than plain pointers and operations with them are expensive. This impact is greater in Sobel (20%) compared to gravitational fish because it contains nine shared accesses per loop iteration. Overall, the communication latency and the overhead from the large number of runtime calls burdens the performance of applications and motivates the presented optimization.

Listing 2.5, presents the computation kernel of the gravitational fish benchmark. The benchmark emulates fish movements based on gravity. The benchmark is an N-Body gravity simulation, using parallel ordinary differential equations [49]. Arrays fish and accel are declared as shared (lines 1-2). Shared arrays or shared objects are accessible from all UPC threads. The layout qualifier [NFISH/THREADS] specified that the shared object is distributed to different UPC threads in blocked form. The construct upc\_forall (line 9) distributes loop iterations among the UPC threads. The fourth expression in the upc\_forall construct is the affinity expression. The affinity expression (&fish[i]) specifies that the owner thread of the specified element executes the *i*th loop iteration.

```

typedef struct fh { double x; double vx;

double y; double vy; } fish_t;

3

typedef struct f_acc { double ax; double ay; } fish_accel_t;

5

shared [NFISH/THREADS] fish_t fish[NFISH];

6

shared [NFISH/THREADS] fish_accel_t acc[NFISH];

7

8

for each time step {

9

/* Phase 1: Force calculation */

upc_forall (i=0; i<NFISH; ++i; &fish[i]) {</pre>

10

11

tmpx = tmpy = 0;

12

for (j = 0; j < NFISH; ++j) {</pre>

13

dx = fish[j].x - fish[i].x;

dy = fish[j].y - fish[i].y;

14

a = calculate_force(dx,dy);

15

16

tmpx += a * dx / r; tmpy += a * dy / r;

17

acc[i].ax = tmpx; acc[i].ay = tmpy;

18

19

20

upc_barrier ();

21

22

}

```

Listing 2.5: UPC version of gravitational Fish.

Runtime calls are responsible for fetching, or modifying, the requested data. Each runtime call may imply communication of one element of the array, leading to fine-grained communication, which in turn leads to poor performance. The compiler transforms each shared access to runtime calls. Read accesses are translated into a \_\_ptr\_deref runtime call, while the write accesses translate into \_\_ptr\_assign. Each runtime call can have various arguments, including the offset of shared variable and the element size. At its turn, internally a PGAS runtime

takes care of accessing the data, which can be in a remote node and so it may imply communication, a *get* or a *put*, depending if you are reading or writing. Before the accessing shared pointers, the compiler also creates calls for shared pointer arithmetic (*\_-ptr\_arithmetic*) as shown in Listing 2.6. The shared pointer is a fat pointer that contains information about the offset, the thread, and the allocated size. Note, that when the compiler knows the number of the UPC threads, it can eliminate the pointer arithmetic call and replace it with shifts and masks.

```

1

for each time step {

2

3

/* Phase 1: Force calculation */

4

upc_forall (i=0; i<NFISH; ++i; &fish[i]) {</pre>

5

tmpx = tmpy = 0;

6

for (j = 0; j < NFISH; ++j) {</pre>

__ptr1 = __ptr_arithmetic( &fish[j].x, ...);

7

8

__tmp1 = __ptr_dereference( ptr1, ...);

9

__ptr2 = __ptr_arithmetic( &fish[j].y, ...);

10

__tmp2 = __ptr_dereference( ptr2, ...);

11

__ptr3 = __ptr_arithmetic( &fish[i].x, ...);

12

__tmp3 = __ptr_dereference( ptr3, ...);

13

__ptr4 = __ptr_arithmetic( &fish[i].y, ...);

14

__tmp4 = __ptr_dereference( ptr4, ...);

15

16

dx = _{tmp1} - _{tmp3}; dy = _{tmp2} - _{tmp4};

a = calculate_force(dx,dy);

17

18

tmpx += a * dx / r; tmpy += a * dy / r;

19

20

_{\text{tmp5}} = \text{tmpx};

21

__ptr5 = __ptr_arithmetic( &acc[i].ax, ...);

22

__ptr_assign( &__tmp5, ptr5, ...);

23

_{\text{tmp6}} = \text{tmpy};

24

__ptr6 = __ptr_arithmetic( &acc[i].ay, ...);

25

__ptr_assign( &__tmp6, ptr6, ...);

26

27

upc_barrier ();

28

29

}

30

```

Listing 2.6: Final form of the source code.

The PGAS programming model boosts programmer productivity by providing shared variables for inter-process communication instead of message passing [16, 17, 18]. However, the performance of these emerging languages has room for improvement. Today, PGAS programs deliver scalable performance on clusters only when they are well written. In previous work, many researchers have pointed out the bottlenecks of PGAS languages [19, 20, 51]. Some reasons for the limited PGAS performance are:

Figure 2.4: XL UPC compiler framework.

- The low communication efficiency of fine-grained accesses data accesses.

- The absence of non-blocking communication mechanisms on PGAS languages. Blocking communication mechanisms eliminate any possible opportunity for computation and communication overlap.

- The existence of function calls for accessing shared data and the absence of inter-procedural analysis. They disable common compiler loop optimizations because they reduce the scope of many data-flow optimizations such as copy propagation and common sub-expression elimination.

- Transparency of shared accesses leads to possible hotspot creation on the network.

#### 2.4 The IBM UPC Compiler and Runtime System

This section presents the XL UPC compiler framework [52, 53] used to implement the optimization. The XL UPC compiler has three main components: (i) the Front End (FE); (ii) the Toronto Portable Optimizer (TPO) high-level optimizer; (iii) a low-level optimizer (TOBEY). Figure 2.4 shows the role of each component in the compilation of UPC programs.

#### 2.4.1 XL UPC Compiler Framework

The XL UPC compiler has three main components: (i) the Front End (FE) transforms the UPC source code to an intermediate representation (W-Code); (ii) the Toronto Portable Optimizer (TPO) high-level optimizer performs machine independent optimizations for UPC and C/C++ languages; (iii) and a low-level optimizer performs machine-dependent optimizations.

The compiler front end tokenizes and parses UPC source code, performs syntactic and semantic analysis, and diagnoses violations of the Unified Parallel C (v 1.2) language rules. It then generates an intermediate language representation (IR) of the UPC program, augmented with UPC extensions such as the layout of shared arrays, and the affinity expression of a upc\_forall loop, for example. The augmented intermediate representation (W-Code + UPC extensions) is consumed by the high-level optimizer, or TPO (Toronto Portable Optimizer). The high-level optimizer component has been extended to perform UPC specific optimizations; it also performs a subset of the traditional control-flow, data-flow and loop optimizations designed for the C language on UPC source code.

The high-level optimizer interfaces with the PGAS runtime (or XL UPC runtime) through an internal API that is used to translate operations on shared objects such as dereferencing (reading/writing) a pointer to a shared object (such as a shared array for example) and performing pointer arithmetic operations. Finally, the high-level optimizer produces a modified version of the IR (Optimized Wcode) that lacks UPC-specific extensions (operations on UPC extensions are either translated to PGAS runtime calls or resolved to the base IR through optimizations). The IR produced by the high-level optimizer is consumed by the low-level optimizer (TOBEY), which performs further optimizations that are UPC unaware. After optimizing the low level IR, TOBEY generates machine code for the target architecture. This process is repeated for each compilation unit. To complete the compilation process, the XL UPC compiler invokes the system linker, which links compiler-generated objects and any required libraries (such as the PGAS runtime library) to form an executable.

The XL UPC compiler provides a number of UPC specific optimizations. The next part of this section examines the main high level UPC specific optimizations, which are implemented in the XL UPC compiler.

# Shared object access optimizations

The XL UPC compiler implements a set of performance optimizations on shared array accesses. The compiler can partition shared array accesses performed in a upc\_forall work-sharing loop into two categories: shared local accesses (accesses that have affinity with the issuing thread) and shared remote accesses. Shared array accesses that have been proven to have affinity with the issuing thread are optimized by the compiler in such a way as to eliminate unnecessary runtime calls. Shared array accesses that are remote can be coalesced by the compiler to reduce the communication latency.

#### Shared object access privatization

In a typical scenario, the XL UPC compiler translates accesses to shared arrays by generating an appropriate set of runtime function calls. In the context of a upc\_forall loop the compiler can often prove that the memory read and/or

written during an array access operation resides in the local address space of the accessing thread; in such cases the compiler generates code that performs the indexing (pointer arithmetic) operations required to access the shared array directly. To do so, the compiler retrieves the address of the shared array partition in the local address space (the private address space of the accessing thread) via a runtime function call. It moves the runtime call outside the upc\_forall loop nest containing the shared array access being translated. This is legal because the local shared array address is loop-invariant. Finally, the compiler uses the local array address to index the appropriate shared array element, doing any pointer arithmetic operations that are necessary locally [54]. Figure 2.5 presents an example of local shared accesses privatization.

```

Programmer's Code

After transformation

#define SCAL 3.0

shared double a [N]

shared double b [N]

#define SCAL 3.0

shared double c [N] ;

shared double a [N];

void StreamTriad(){

shared double b [N] ;

int i ;

shared double c [N] ;

double *__aBase = __xlupc_base_addr(a) ;

double *__bBase = __xlupc_base_addr(b) ;

void StreamTriad(){

double *__cBase = __xlupc_base_addr(c) ;

int i ;

upc_forall (i=0; i<N; i++; &a[i]){</pre>

upc_forall (i=0;i<N;i++; &a[i]){</pre>

a[i] = b[i] + SCAL * c[i] ;

*( __aBase + OFFSET(i)) =

}

*( __bBase + OFFSET(i)) +

}

SCAL * ( *( __cBase + OFFSET(i)))

}

```

Figure 2.5: Example of privatization optimization.

# Shared object access coalescing

Normally, the XL UPC compiler translates a remote shared array access by generating a call to the appropriate runtime function. For example, reading from (or writing to) multiple shared array elements that have affinity to the same remote thread causes the compiler to generate a runtime call for each of the array elements read. In the context of a upc\_forall loop nest, the compiler can often determine that several array elements are read from the same remote partition. In this case, the compiler combines the read operations and generates a single call to the runtime system to retrieve the necessary elements together, thus reducing the number of communication messages between the accessing thread and the thread that has affinity with the remote array partition [29].

# Shared object remote updating

This optimization targets read-modify-write operations on a shared array element. When translating a read operation followed by a write operation on the same shared array element the compiler normally generates two runtime calls: one to retrieve the shared array element and one to write the modified value back. When the compiler can prove that the array elements being read and written have the same index, it can generate a single runtime call, with which it instructs the runtime system to perform the update operation on the thread that has affinity with the array elements accessed. This optimization reduces the number of calls required to translate the read-modify-write pattern from two to one, and therefore reducing the communication requirement associated with the operation.

# Array idiom recognition

Unified Parallel C programs often include loops that simply copy all elements of a shared array into a local array, or vice versa, or loops used to set all elements of a shared array with an initial value. The XL UPC compiler is able to detect these common initialization idioms and substitute the fine-grained communication in such loops with coarser-grained communication. The compiler achieves this goal by replacing the individual shared array accesses with calls to one of the UPC string handling functions: upc\_memget, upc\_memset, upc\_memcpy, or upc\_memput. Figure 2.6 provides an example of this optimization.

| Programmer's Code                                                                                                       | After transformation                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>#define N 16384 #define BF (N/THREADS)</pre>                                                                       | <pre>#define N 16384 #define BF (N/THREADS)</pre>                                                                                                                      |  |

| <pre>shared [BF] int a[N]; int b[N];</pre>                                                                              | <pre>shared [BF] int a[N]; int b[N];</pre>                                                                                                                             |  |

| <pre>int main () {   int i;   if (MYTHREAD==0) {     for (i=0; i<n; a[i]="b[i];" i++){="" pre="" }="" }<=""></n;></pre> | <pre>int main () {    int i;    if (MYTHREAD==0) {      for (i=0; i<n; &b[i],="" bf*sizeof(b[i]));="" i+="BF)" pre="" upc_memput(&a[i],="" {="" }="" }<=""></n;></pre> |  |

Figure 2.6: Example using the array idiom recognition.

# Parallel loop optimizations

The XL UPC compiler implements a set of optimizations that remove the overhead associated with the evaluation of the affinity expression in a upc\_forall loop. The affinity expression in a upc\_forall loop could be naively translated by using a branch to control the execution of the loop body. For example, an integer affinity expression "i" could be translated by inserting the conditional expression (i == MYTHREAD) around the upc\_forall loop body. The compiler, on the other hand, translates the upc\_forall loop into a for loop (or a for loop nest) using a stripmining transformation technique that avoids the insertion of the affinity branch altogether, and removes a major obstacle to the parallel scalability of the loop. For example, the parallel loop:

```

upc_forall ( i =0; i < N; i ++; i ) {

a[i] = b[i] + scalar * c[i]

}

will be transformed to:

for ( i =0; i < N; i ++) {

if (( i % THREADS) == MYTHREAD )

a[i] = b[i] + scalar * c[i] ;

}</pre>

```

However after the optimization the final loop will not contain the affinity branch:

```

for ( i =MYTHREAD; i <N; i +=THREADS) {

a[i] = b[i] + scalar * c[i] ;

}</pre>

```

## 2.4.2 Runtime

The PGAS runtime provides a platform-independent interface that allows the executable to run in different machines and it is designed for scalability in large parallel machines [55, 54]. Currently supported platforms include: shared-memory multiprocessors using the Pthreads library; Low-level Application Programming Interface [56]; and Parallel Active Messaging Interface (PAMI) [57]. Experimental ports of the UPC runtime also exists for other Messaging systems like Myrinet Express [58], BlueGene/L message layer [59], and Deep Computing Messaging Framework (DCMF) [60]. The PGAS runtime is designed for a hybrid mode of operation on clusters of SMP nodes. For example, UPC threads communicate through shared memory when possible, and they send messages to other nodes through one of several available transports. A similar approach was followed in the GASNet runtime system [61]. The runtime exposes to the compiler an Application Program Interface for managing shared data and synchronization.

#### Memory Management

In UPC, there are two types of memory allocations: *local memory* allocations performed using malloc and which are currently outside of the tracking capability of the runtime, and *shared memory* allocated using UPC specific constructs such as upc\_all\_alloc(), upc\_alloc() and upc\_global\_alloc().

Within the UPC specific family of allocation functions, the runtime currently employs a set of optimizations to help both with remote memory address inference with memory registration. The memory registration pins the memory (no memory swap and no page movement) and notifies the network interface controller (NIC) of the virtual-to-physical address mapping of this memory. The memory registration is necessary to enable the Remote Direct Memory Access (RDMA) mechanisms that are used in high performance machines. First, shared arrays allocated using upc\_all\_alloc() are allocated symmetrically at the same virtual memory address on all locations. In doing so, the XL UPC allocator creates a reserved area in the virtual address space of each process called the symmetric partition. The starting virtual address of each symmetric partition, called the origin, is identical across all threads and distributed shared arrays are then stored in blocks of memory located isomorphically in each symmetric partition. The READ and WRITE operations on elements of a shared array allocated with upc\_all\_alloc, therefore, know the virtual address in the remote locations. Shared memory allocated using the upc\_global\_alloc primitive is handled in a similar fashion.

The users can declare shared arrays allocated in one thread's address space using upc\_alloc. In this situation, other threads can only obtain references to these arrays using another explicit data exchange. If such a reference is obtained, a remote thread can perform remote reads or writes to the data of the shared array. In the current XL UPC implementation, the memory allocated using upc\_alloc is not registered with PAMI. If the upc\_memput access or upc\_memget access memory that explicitly allocated with system malloc, then the runtime uses active messages. For example, in upc\_memput call, the destination must always be a shared memory array while the source can actually be from an array allocated with malloc.

# Point to point data transfers

Point to point data transfers are employed by UPC whenever a remote array index is accessed or whenever upc\_memput/upc\_memget are invoked. The underlying network supports three modes of data transfer, which are referred to as active messages with short, large data, and RDMA. The XL UPC runtime system exploits all three modes.

The runtime enforces the ordering constraints imposed by the UPC memory consistency model. The underlying interconnect and PAMI library do not preserve the order of messages between a source and destination process. For this reason, when mapping UPC constructs to PAMI primitives, the runtime explicitly waits for a message to be remotely delivered before sending the next message to the same

destination. However, the runtime can send a message to a different destination without waiting for the acknowledgement of messages on previous destinations. While this can be seen as a performance bottleneck, in practice this decision did not affect the performance of most benchmarks. This is because often the threads send to different destinations before sending again to a particular one.

# **Atomic Operations**

The XL Unified Parallel C compiler implements the atomic extension of the Unified Parallel C language as proposed by Berkeley UPC [62]. This extension, which is on track to being adopted as part of the UPC 1.3 specification, allows users to atomically read and write private and shared memory in a UPC program. With atomic functions, you can update variables within a synchronization phase without using a barrier. The atomic functions are included in List 2.7. The function prototypes have different variants depending on the values of type, X, and RS. X and type can take any pair of values in (I, int), (UI, unsigned int), (L, long), (UL, unsigned long), (I64,int64\_t), (U64,uint64\_t), (I32,int32\_t), (U32,uint32\_t). RS can be either 'strict' or 'relaxed'.

Listing 2.7: XL UPC Atomics Interface.

## **Accelerated Collectives**

UPC collectives are implemented completely within the runtime system. The compiler redirects UPC calls to runtime entries with only some minimal analysis in certain situations. In turn, the runtime transforms UPC pointers-to-shared to regular pointers and calls appropriate collectives within PAMI.

## Other Runtime Optimizations

On a platform that supports simultaneous multithreading, thread binding turns out to be crucial. The runtime system provides flexible control on how to bind UPC threads to hardware threads. By default, no binding is performed while a specific mapping is performed with proper command line arguments. The autobinding option is recommended. Huge memory pages usage is another runtime option, which instructs the memory allocator to use huge memory pages.

# Chapter 3

# Experimental Setup

This chapter explores characteristics of hardware environment, and the benchmarks used in the evaluation. The hardware description provides information about the hardware in a single node and presents the interconnect network. Furthermore, this section presents an evaluation of some key performance characteristics, such as latency, all-to-all and point-to-point bandwidth. The benchmark section introduces the available microbenchmarks and benchmarks used later in this work.

# 3.1 The hardware environment

This dissertation uses the POWER7-IH (or IBM® Power® 775) scalable High Performance Computing platform [63] for the evaluation. This platform consists of a number of POWER7® [64, 65] nodes, connected using the POWER7® Hub interconnect [66]. The entire system, including the processors, memories, and interconnect, is water cooled. The water dissipates the thermal waste by circulating components over the system and it is exchanged with the facility's chilled water.

Each node has four chips which constitute a 32-core Symmetric Multiprocessor (SMP) node. Chips are directly connected to each other at a peak of 48 GB/s. The POWER7 processor has 32 KBytes instruction and 32 KBytes L1 data cache per core, 256 KBytes 2nd level per core, and a 32 MByte 3rd level cache shared per chip. Each core is equipped with four SMT threads and 12 execution units. The peak performance of each P7-IH chip is 246 GFlops/s resulting in a peak of 984 GFlops/s on each node. The POWER7 processor implements efficient adaptive power management techniques compared to predecessors of PowerPC CPU family [67]. The microarchitecture implements a set of integer and floating point SIMD instructions, referred to as Vector Scalar eXtensions. Finally, each chip has two memory controllers supporting a total of eight DDR-3 memory channels. The size of available main memory is 128 GBytes per node.

The machine is organized in drawers. Each drawer consists of eight nodes, adding up one TByte of memory and 7,87 Tflop/s. Four drawers are connected

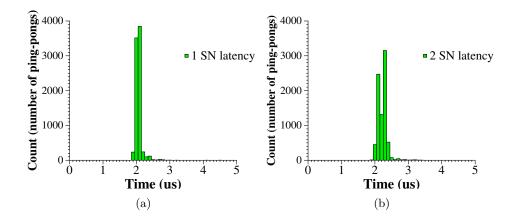

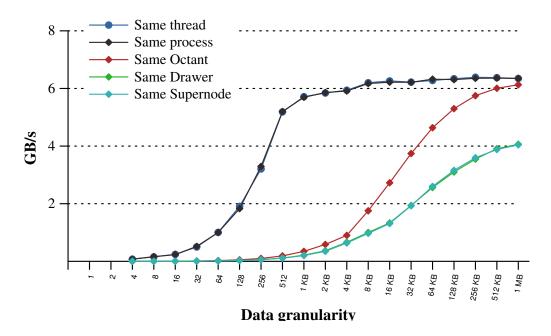

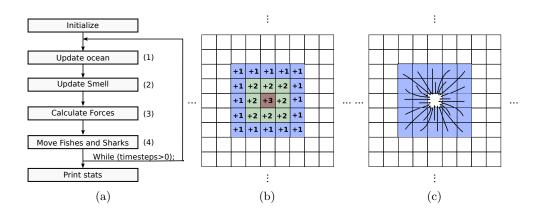

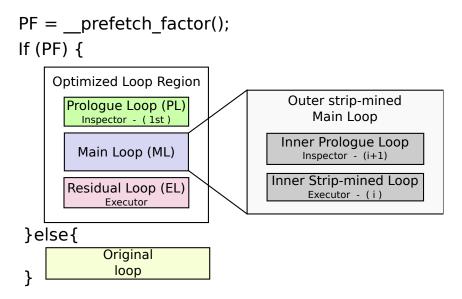

Figure 3.1: Architecture of the machine.