Universidade Estadual de Campinas Instituto de Computação

Juan Jesús Salamanca Guillén

## Thread-Level Speculation on Hardware Transactional Memory Architectures

Especulação de Threads usando Arquiteturas de Memória Transacional em Hardware

CAMPINAS 2016

#### Juan Jesús Salamanca Guillén

#### Thread-Level Speculation on Hardware Transactional Memory Architectures

#### Especulação de Threads usando Arquiteturas de Memória Transacional em Hardware

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutor em Ciência da Computação.

Dissertation presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

#### Supervisor/Orientador: Prof. Dr. Guido Costa Souza de Araújo Co-supervisor/Coorientador: Prof. Dr. José Nelson Amaral

Este exemplar corresponde à versão final da Tese defendida por Juan Jesús Salamanca Guillén e orientada pelo Prof. Dr. Guido Costa Souza de Araújo.

#### CAMPINAS 2016

Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

| Sa31t | Salamanca Guillén, Juan Jesús, 1988-<br>Thread-level speculation on hardware transactional memory architectures /<br>Juan Jesús Salamanca Guillén. – Campinas, SP : [s.n.], 2016.                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Orientador: Guido Costa Souza de Araújo.<br>Coorientador: José Nelson Amaral.<br>Tese (doutorado) – Universidade Estadual de Campinas, Instituto de<br>Computação.                                                                                                                                     |

|       | 1. Especulação no nível de threads. 2. Memória transacional. 3.<br>Processamento paralelo (Computadores). 4. Threads (Programa de<br>computador). I. Araújo, Guido Costa Souza de,1962 II. Amaral, José<br>Nelson,1964 III. Universidade Estadual de Campinas. Instituto de<br>Computação. IV. Título. |

Informações para Biblioteca Digital

Título em outro idioma: Especulação de threads usando arquiteturas de memória transacional em hardware Palavras-chave em inglês: Thread-level speculation Transactional memory Parallel processing (Electronic computers) Threads (Computer programs) Área de concentração: Ciência da Computação Titulação: Doutor em Ciência da Computação Banca examinadora: Guido Costa Souza de Araújo [Orientador] Alexandro José Baldassin Márcio Bastos Castro Sandro Rigo Emilio de Camargo Francesquini Data de defesa: 21-12-2016 Programa de Pós-Graduação: Ciência da Computação

Universidade Estadual de Campinas Instituto de Computação

#### Juan Jesús Salamanca Guillén

#### Thread-Level Speculation on Hardware Transactional Memory Architectures

#### Especulação de Threads usando Arquiteturas de Memória Transacional em Hardware

#### Banca Examinadora:

- Prof. Dr. Guido Costa Souza de Araújo IC/UNICAMP

- Prof. Dr. Alexandro José Baldassin IGCE/UNESP

- Prof. Dr. Márcio Bastos Castro INE/UFSC

- Prof. Dr. Sandro Rigo IC/UNICAMP

- Dr. Emilio de Camargo Francesquini IC/UNICAMP

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 21 de dezembro de 2016

# Dedication

This work is dedicated to my dear mother, Flavia Guillén.

# Acknowledgements

First and foremost, I would like to thank God and my beloved son Juan Pablo Matías for their love. I would also like to thank my mother, Flavia, for encouraging me to pursue my dreams and for her tremendous support in each step of my life. I would like to thank my brother Jesús and my sisters Ana Flavia and Jennifer for their friendship, affection, and confidence. I would like to thank all my family, especially my father Jesús, my grandmother Elsa, and my aunt Yemile, who were always supporting me and encouraging me with their best wishes.

I will always be grateful to my supervisor, Guido Araújo, for believing in me and for all the incentive, support, and patience throughout our project. You became more than a supervisor, you became a friend and a second father. Through a number of difficult times, you were very supportive and understanding. Thank you, Guido. I thank my cosupervisor Nelson Amaral for his support, for always helping me think outside the box, and for welcoming me in Canada. Nelson, meeting you and working with you proved to be an invaluable experience. I am very grateful to both for their guidance to learn about a research career.

I thank all my dear friends, especially Renzo, Luis, Edmanuel, Pepe, José Manuel, Lucas, Laura, Ticiana, and Martin, for being always there. Also, I want to thank all my friends of the Institute of Computing at UNICAMP as well as of the Department of Computing Science at the University of Alberta, whose friendship have made both incredible places to study, to learn, and to have a good time.

Finally, I would like to thank CNPq, Samsung, CAPES, LGE, and FAPESP (grants 15/04285-5 and 15/12077-3) for their financial support to this work.

# Resumo

Especulação no nível de threads (TLS) é uma técnica em hardware/software que possibilita a execução paralela de múltiplas iterações de um laço, inclusive na presença de algumas dependências loop-carried. TLS exige mecanismos em hardware para auxiliar a detecção de conflitos, o armazenamento especulativo, os commits das transações em ordem, e o roll-back das transações. Trabalhos anteriores exploraram enfoques para implementar TLS, tanto em hardware dedicado como puramente em software, e tentaram predizer o desempenho de futuras implementações de TLS em hardware. Contudo, não existe nenhum processador comercial que forneça suporte direto para TLS. Entretanto, execução especulativa é suportada na forma de Memória Transacional em Hardware (HTM) — disponível em processadores modernos como Intel Core e IBM POWER8. HTM implementa três características essenciais para TLS: detecção de conflitos, armazenamento especulativo, e roll-back de transações.

Antes de aplicar TLS a um laço quente, é necessário determinar se o laço tem potencial para ser especulado. Um laço pode ser adequado para TLS se a probabilidade de dependências loop-carried em tempo de execução for baixa; para estimar esta probabilidade um perfilamento de dependências do laço deve ser usado. Este trabalho apresenta um verificador das dependências loop-carried integrado como uma nova extensão de OpenMP, a diretiva **parallel for check**, a qual pode ser usada para ajudar desenvolvedores a identificarem a existência destas dependências em construções **parallel for**.

Este trabalho também apresenta uma análise detalhada da aplicação de HTM para a paralelização de laços com TLS e descreve uma avaliação cuidadosa da implementação de TLS usando HTMs disponíveis em processadores modernos. Como resultado, esta tese proporciona evidências para validar várias afirmações importantes sobre o desempenho de TLS nestas arquiteturas. Os resultados experimentais mostram que TLS usando HTM produz speedups de até  $3.8 \times$  para alguns laços.

Finalmente, este trabalho descreve uma nova técnica de especulação para a otimização, e execução simultânea, de múltiplos traços de regiões de código quente. Esta técnica, chamada Speculative Trace Optimization (STO), enumera, otimiza, e executa especulativamente traços de laços quentes. Isto requer o suporte em hardware disponível em sistemas HTM. Este trabalho discute as características necessárias para suportar STO: multi-versão, resolução de conflitos tardia, detecção de conflitos prematura, e sincronização das transações. Uma revisão das arquiteturas HTM existentes — Intel TSX, IBM BG/Q, e IBM POWER8 — mostra que nenhuma delas tem todas as características requeridas para implementar STO. Entretanto, este trabalho mostra que STO pode ser implementado nas arquiteturas HTM existentes através da adição de privatização e código para esperar/retomar.

## Abstract

Thread-Level Speculation (TLS) is a hardware/software technique that enables the execution of multiple loop iterations in parallel, even in the presence of some loop-carried dependences. TLS requires hardware mechanisms to support conflict detection, speculative storage, in-order commit of transactions, and transaction roll-back. Prior research has investigated approaches to implement TLS, either on dedicated hardware or purely in software, and has attempted to predict the performance of future TLS hardware implementations. Nevertheless, there is no off-the-shelf processor that provides direct support for TLS. Speculative execution is supported, however, in the form of Hardware Transactional Memory (HTM) — available in recent processors such as the Intel Core and the IBM POWER8. HTM implements three key features required by TLS: conflict detection, speculative storage, and transaction roll-back.

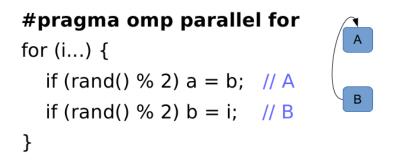

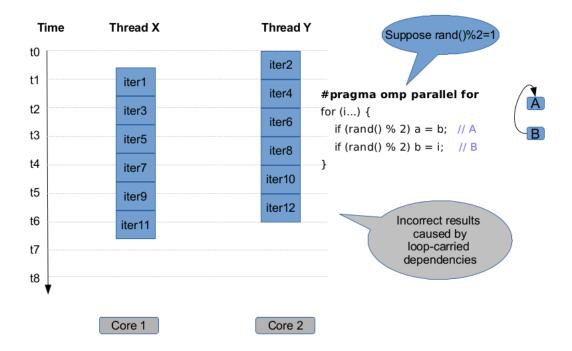

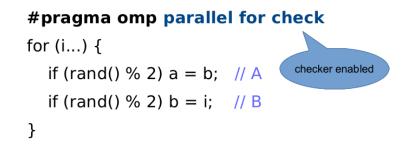

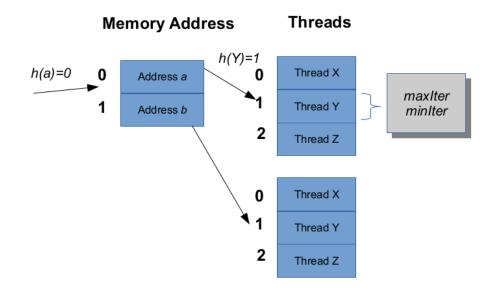

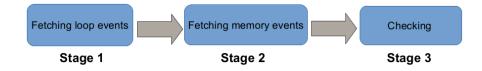

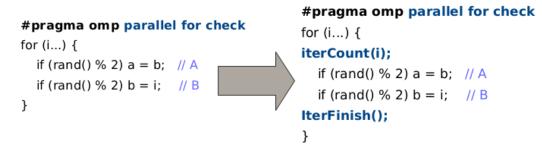

Before applying TLS to a hot loop, it is necessary to determine if the loop has potential to be amenable. A loop could be amenable if the probability of loop-carried dependences at runtime is low; to measure this probability loop dependence profiling is used. This project presents a novel dynamic loop-carried dependence checker integrated as a new extension to OpenMP, the **parallel for check** construct, which can be used to help programmers identify the existence of loop-carried dependences in **parallel for** constructs.

This work also presents a detailed analysis of the application of HTM support for loop parallelization with TLS and describes a careful evaluation of the implementation of TLS on the HTM extensions available in such machines. As a result, it provides evidence to support several important claims about the performance of TLS over HTM in the Intel Core and the IBM POWER8 architectures. Experimental results reveal that by implementing TLS on top of HTM, speed-ups of up to  $3.8 \times$  can be obtained for some loops.

Finally, this work describes a novel speculation technique for the optimization, and simultaneous execution, of multiple alternative traces of hot code regions. This technique, called Speculative Trace Optimization (STO), enumerates, optimizes, and speculatively executes traces of hot loops. It requires hardware support that can be provided in a similar fashion as that available in HTM systems. This work discusses the necessary features to support STO, namely multi-versioning, lazy conflict resolution, eager conflict detection, and transaction synchronization. A review of existing HTM architectures — Intel TSX, IBM BG/Q, and IBM POWER8 — shows that none of them has all the features required to implement STO. However, this work demonstrates that STO can be implemented on top of existing HTM architectures through the addition of privatization and wait/resume code.

# List of Figures

| $2.1 \\ 2.2$                                                          | A loop with two <i>may</i> loop-carried dependences. Adapted from [40] Code of each thread to parallelize Figure 2.1's loop with TLS on ideal HTM | 22                         |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.3                                                                   | system                                                                                                                                            | 23<br>23                   |

| $3.1 \\ 3.2$                                                          | HELIX Execution flow of Figure 2.1. Sequential segments are synchronized. Dependence in pass_flag in 179.art.                                     | 27<br>31                   |

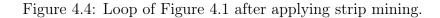

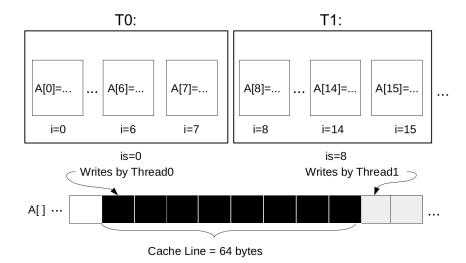

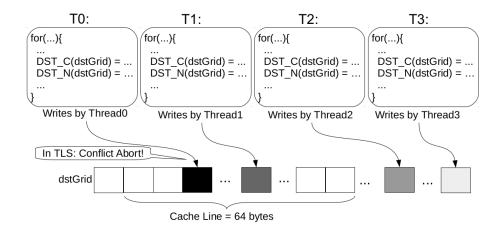

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$ | Figure 2.1. A loop with two <i>may</i> loop-carried dependences Parallelization of Figure 4.1 with four threads                                   | 35<br>36<br>36<br>37<br>37 |

| 4.7                                                                   | and TSX HTM systems                                                                                                                               | 39<br>40                   |

| 4.8                                                                   | <b>1</b> bm hot loop                                                                                                                              | 40                         |

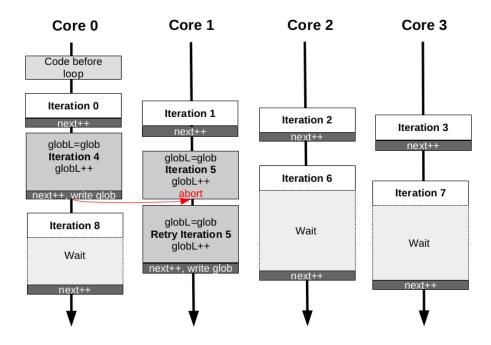

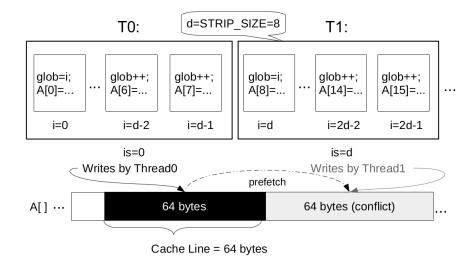

| 4.9                                                                   | False sharing due to non-consecutive writes in the array dstGrid                                                                                  | 41                         |

| 4.10                                                                  | False sharing due to prefetching in TSX                                                                                                           | 42                         |

|                                                                       | mcf's hottest loop.                                                                                                                               | 44                         |

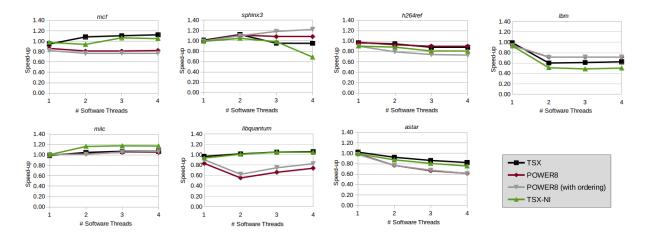

| 4.12                                                                  | Speed-ups for TLS execution on TSX, POWER8, POWER8 with ordering (tsuspend/tresume), and TSX-NI.                                                  | 45                         |

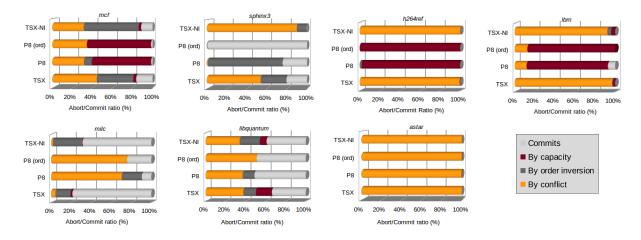

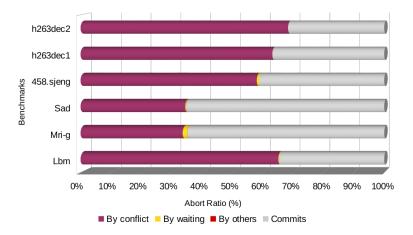

| 4.13                                                                  | Abort/Commit ratio by TLS execution with 4 threads on TSX, POWER8, POWER8 with ordering (tsuspend/tresume), and TSX-NI. Abort reasons are shown.  | 45                         |

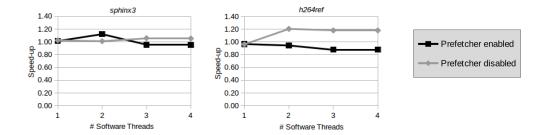

| 4.14                                                                  | Speed-ups for sphinx3 and h264ref by TLS execution on TSX with prefetcher enabled/disabled.                                                       | 46                         |

| 4.15                                                                  | h264ref's hottest loop                                                                                                                            | 46                         |

| 4.16                                                                  | sphinx3's hottest loop                                                                                                                            | 47                         |

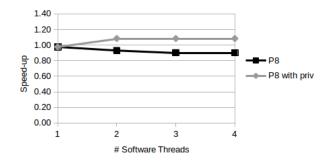

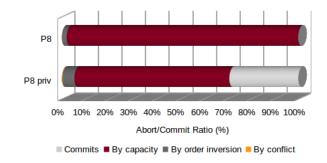

| 4.17                                                                  | Speed-ups for h264ref by TLS execution on POWER8 with and without privatization.                                                                  | 48                         |

| 4.18                                                                  | Abort/Commit ratio for h264ref by TLS execution with 4 threads on POWER8 with and without privatization.                                          | 49                         |

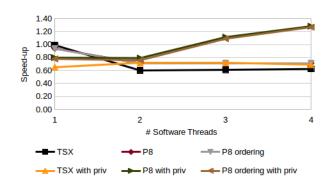

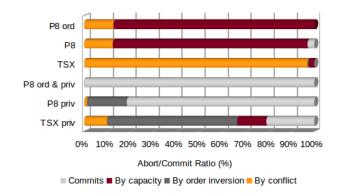

| 4.19                                                                  | Speed-ups for 1bm by TLS execution on TSX, POWER8, and POWER8                                                                                     |                            |

| 4.20                                                                  | with ordering, with and without privatization                                                                                                     | 49                         |

| 4.21                                                                  | POWER8, and POWER8 with ordering, with and without privatization<br>Speed-ups for sphinx3 by TLS execution on TSX and POWER8 for dif-             | 50                         |

|                                                                       | ferent strip sizes with 2 and 4 threads respectively.                                                                                             | 50                         |

| 5.1          | loopA and loopF                                                                                    | 55       |

|--------------|----------------------------------------------------------------------------------------------------|----------|

| 5.2          | loopF after applying strip mining and dividing into two components                                 | 56       |

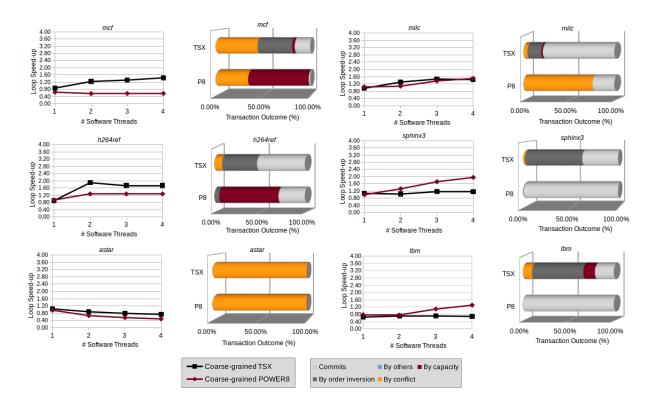

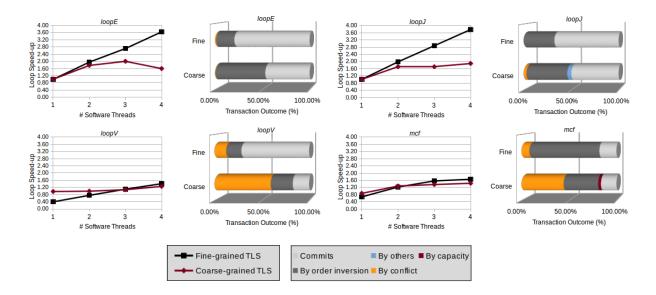

| 5.3          | Class I. Speed-ups and Abort ratios for coarse-grained TLS execution on TSX and POWERS             | 57       |

| 5 4          | TSX and POWER8.                                                                                    |          |

| 5.4          | loopE, loopJ, and loopR.                                                                           | 58       |

| 5.5          | Class II. Speed-ups and Abort ratios for coarse-grained TLS execution on                           | 50       |

| <b>F</b> 0   | TSX and POWER8.                                                                                    | 59       |

| 5.6          | Class III and Others. Speed-ups and abort ratios for coarse-grained TLS                            |          |

|              | execution on TSX and POWER8                                                                        |          |

| 5.7          | loopQ and loopV                                                                                    |          |

| 5.8          | loopP and loopS                                                                                    | 61       |

| 5.9          | loopT and loopU                                                                                    | 62       |

| 5.10         | SPEC2006 Loops. Speed-ups and abort ratios for coarse-grained TLS exe-<br>cution on TSX and POWER8 | 66       |

| 5.11         | Figure 2.1. A loop with two <i>may</i> loop-carried dependences                                    | 66       |

|              | Fine-grained Speculation Execution flow of Figure 5.11.                                            |          |

| 5.13         | mcf's hottest loop.                                                                                | 67       |

|              | Fine-grained TLS without strip mining for mcf's hottest loop.                                      |          |

|              | DDG of mcf's hottest loop                                                                          | 68       |

|              | SCCs of the DDG of Figure 5.15.                                                                    |          |

|              | Fine-grained TLS with strip mining in restructured mcf's hottest loop.                             |          |

|              | Privatization in basket_size is shown.                                                             | 70       |

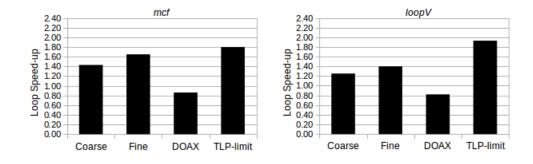

| 5.18         | Speed-ups in mcf's hottest loop and loopV using fine-grained TLS on Intel Core.                    | 70       |

| 5.19         | Speed-ups and Abort ratios for fine-grained TLS execution on Intel Core                            |          |

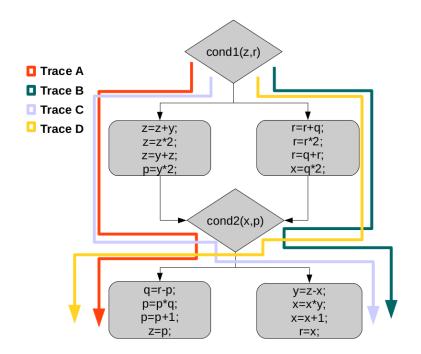

| 6.1          | Example of code to optimize.                                                                       | 73       |

| 6.2          | Possible traces of execution.                                                                      |          |

| 6.3          | Traces as transactions.                                                                            |          |

| 6.4          | Optimized traces of execution.                                                                     |          |

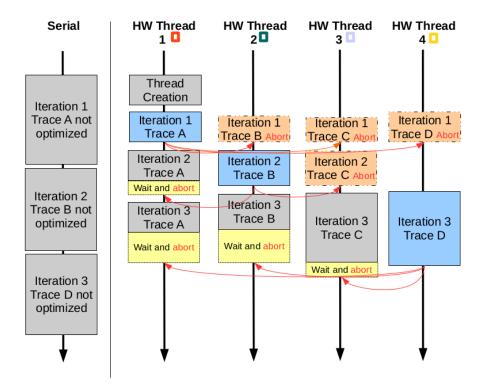

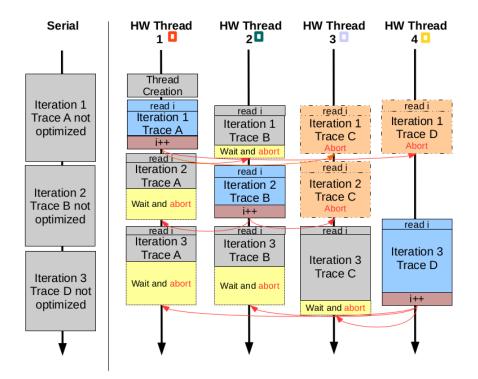

| 6.5          | Possible execution flow of STO Traces shown in Figure 6.4 on ideal HTM.                            | 75<br>76 |

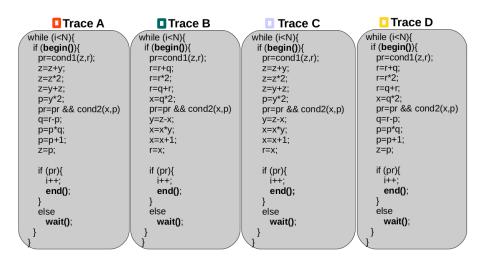

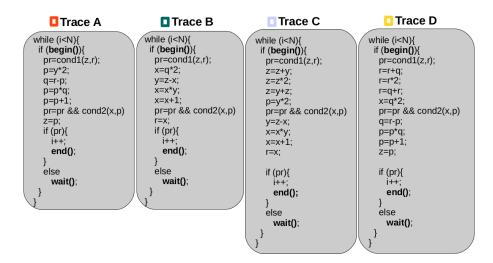

| 0.5<br>6.6   | Modified Source Code of Trace A                                                                    | 70<br>78 |

| 6.7          |                                                                                                    | 81       |

| 0.7<br>6.8   | Possible execution flow of STO Traces shown in Figure 6.4 on Intel TSX                             | 84       |

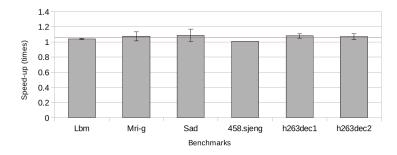

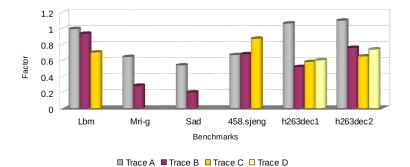

|              | Speed-ups of benchmarks with respect to serial execution. $\ldots$ $\ldots$ $\ldots$               |          |

| 6.9          | Abort Ratio (%) of the benchmarks. $\ldots$                                                        | 84       |

| 6.10         | Factor for each trace in the benchmarks                                                            | 85       |

| 7.1          | Loop-carried dependence example                                                                    | 86       |

| 7.2          | Possible execution flow of the loop of Figure 7.1.                                                 |          |

| 7.3          | Usage of <i>check</i> construct in the program of Figure 7.1.                                      | 87       |

| 7.4          | Multilevel Hash Table mapping to a memory reference in <i>address a</i> stored                     | 01       |

| 1.1          | by thread Y                                                                                        | 89       |

| 7.5          | OpenMP checker exploits pipeline level parallelism (3 stages).                                     |          |

| 7.6          | Imaginary source file with the <i>check</i> construct                                              | 91       |

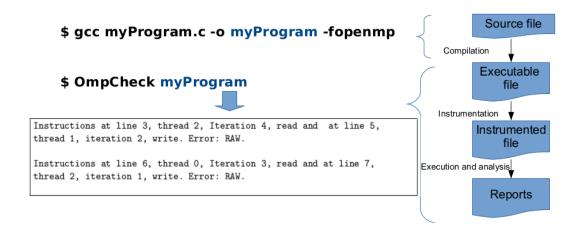

| $7.0 \\ 7.7$ | Flow overview of the <i>OpenMP checker</i> with GCC/Pin.                                           | 91<br>92 |

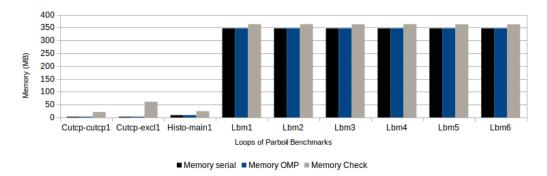

| 7.8          | Memory footprint of three Parboil Benchmarks ( <i>Cutcp</i> , <i>Histo</i> and <i>Lbm</i> )        | 94       |

| 1.0          | executed <i>serially</i> , with <i>OpenMP</i> , and with <i>check</i> modifying different hottest  |          |

|              | loops.                                                                                             | 93       |

|              | 100pp                                                                                              | 30       |

| 7.9  | Memory footprint of five Parboil Benchmarks (Mri-gridding, Mri-q, Spmv,       |    |

|------|-------------------------------------------------------------------------------|----|

|      | Stencil and Tpacf) executed serially, with OpenMP, and with check mod-        |    |

|      | ifying different hottest loops                                                | 93 |

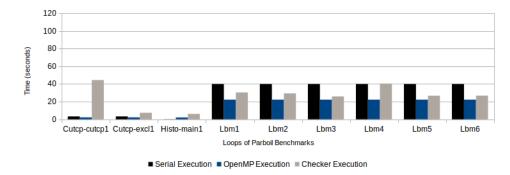

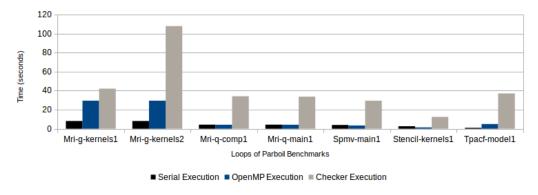

| 7.10 | Execution time of loops of three Parboil benchmarks.                          | 94 |

| 7.11 | Execution time of loops of five Parboil benchmarks.                           | 95 |

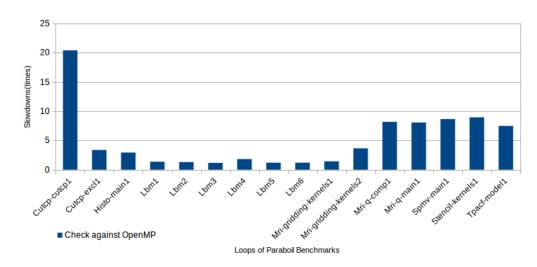

| 7.12 | Slowdowns of loops of Parboil benchmarks using <i>check</i> respect to OpenMP |    |

|      | execution                                                                     | 95 |

# List of Tables

| 2.1 | HTM implementations of Intel Core and IBM POWER [41]                                    | 20 |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.2 | HTM Architectural Features.                                                             | 20 |

| 4.1 | Impact of false sharing on sphinx3                                                      | 37 |

| 4.2 | Loop Characterization in Benchmarks.                                                    | 43 |

| 4.3 | Privatization Results                                                                   | 48 |

| 5.1 | Loops extracted from cBench applications.                                               | 53 |

| 5.2 | Characterization and TLS Execution of Classes                                           | 54 |

| 5.3 | Characterization of 6 loops from SPEC CPU 2006                                          | 64 |

| 5.4 | TLS Execution for 6 loops from SPEC CPU 2006                                            | 65 |

| 6.1 | HTM Architectures.                                                                      | 79 |

| 6.2 | Amenable loops to STO                                                                   | 83 |

| 6.3 | Conflict aborts and commits of Lbm traces.                                              | 84 |

| 7.1 | Verification of 8 Parboil executed with <i>check</i> modifying different hottest loops. | 94 |

# Contents

| 1        | Intr     | oducti  | on                                                                | 15              |

|----------|----------|---------|-------------------------------------------------------------------|-----------------|

| <b>2</b> | Bac      | kgrour  | nd                                                                | 19              |

|          | 2.1      |         | actional Memory                                                   | 19              |

|          | 2.2      |         | Core and IBM POWER8                                               | 20              |

|          | 2.3      | Threa   | d-Level Speculation                                               | 21              |

|          | 2.4      |         | Mining                                                            | 23              |

|          | 2.5      |         | Peeling                                                           | 24              |

|          | 2.6      | -       |                                                                   | 24              |

|          | 2.7      |         | izations using Traces                                             | 24              |

| 3        | Rela     | ated W  | Vork                                                              | 25              |

| 0        | 3.1      |         | d-Level Speculation                                               | $\frac{-5}{25}$ |

|          | 3.2      |         | ative Execution of Loops with Transient Dependences               | $\frac{-6}{26}$ |

|          | 3.3      | -       | lative Trace Optimization                                         | $\frac{-0}{28}$ |

|          | 3.4      | -       | Dependence Profilers                                              | 30              |

|          | 0.1      | 3.4.1   | Pairwise Method                                                   | 31              |

|          |          | 3.4.2   | Stride-based Method                                               | 32              |

| 4        | Eva      | luating | g and Improving TLS in HTMs                                       | <b>34</b>       |

| -        | 4.1      | -       | Carried Dependences and False Sharing                             | 34              |

|          | 4.2      |         | n top of HTM                                                      | 37              |

|          | 4.3      |         | Sharing Effects on TLS                                            | 40              |

|          | 1.0      | 4.3.1   | Capacity Overflow of Transactions                                 | 40              |

|          |          | 4.3.2   | Non-consecutive Writes Within Transactions                        | 41              |

|          |          | 4.3.3   | TSX Cache-line-prefetcher Issues                                  | 41              |

|          | 4.4      |         | iments                                                            | 42              |

|          | 4.4      | 4.4.1   | Benchmarks and Settings                                           | $42 \\ 42$      |

|          |          | 4.4.1   | Results                                                           | 42<br>44        |

| _        | <b>.</b> |         |                                                                   |                 |

| 5        |          | -       | Evaluation of TLS in off-the-shelf HTMs                           | 52              |

|          |          |         | marks, Methodology and Experimental Setup                         | 52              |

|          | 5.2      |         | fication of Loops Based on TLS Performance                        | 55              |

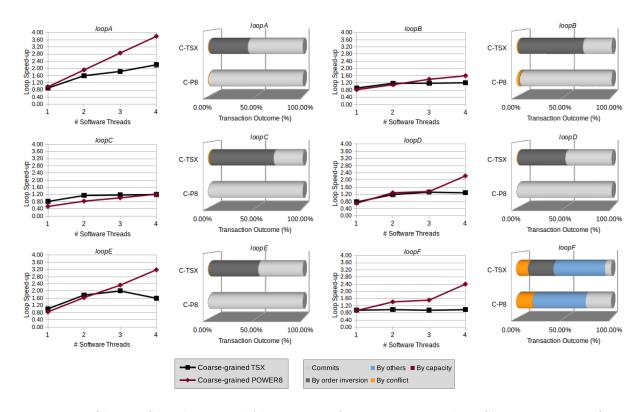

|          |          | 5.2.1   | Class I: Low speculative demand and better performance in POWER8  | 56              |

|          |          | 5.2.2   | Class II: High speculative demand and better performance in Intel |                 |

|          |          |         | Core                                                              | 58              |

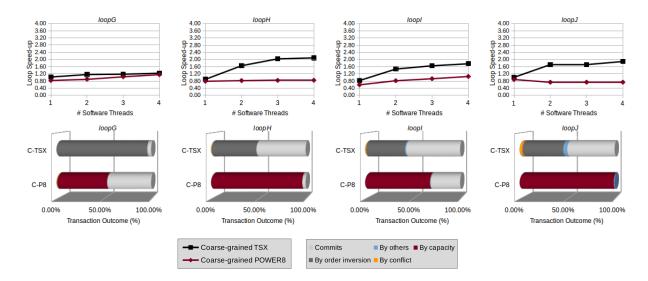

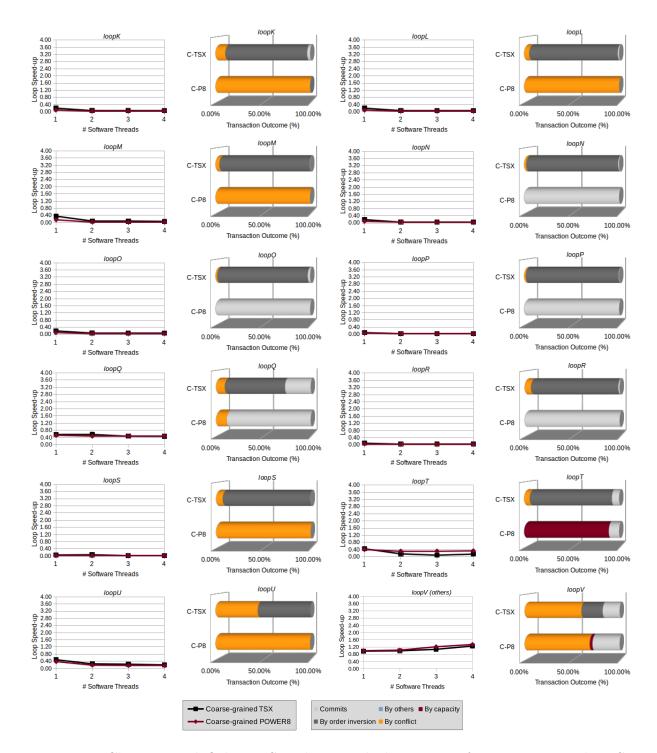

|          |          | 5.2.3   | Class III: Not enough work to be parallelized with TLS            | 59              |

|          |          | 5.2.4   | Others                                                            | 63              |

|          |          | 5.2.5   | Predicting the TLS Performance for Other Loops                    | 65              |

|    | 5.3   | Fine-grained TLS on top of HTM                              | 65 |

|----|-------|-------------------------------------------------------------|----|

| 6  | Usir  | ng HTM to Enable STO                                        | 72 |

|    | 6.1   | Speculative Trace Optimization Supported by HTM             | 72 |

|    |       | 6.1.1 STO on Ideal HTM                                      | 73 |

|    |       | 6.1.2 STO Prototype on Real-world HTM                       | 77 |

|    |       | 6.1.3 Running STO on Intel TSX                              | 80 |

|    | 6.2   | Performance Assessment of Proof-of-Concept Prototype        | 81 |

|    |       | 6.2.1 Benchmarks, Implementation, Settings, and Environment | 82 |

|    |       | 6.2.2 Benchmark Results                                     | 82 |

| 7  | para  | allel for check Directive                                   | 86 |

|    | 7.1   | Check Construct in OpenMP                                   | 87 |

|    |       | 7.1.1 Overview of the Algorithm                             | 87 |

|    |       | 7.1.2 Parallelization of the Algorithm                      | 89 |

|    | 7.2   | Implementation                                              | 90 |

|    |       | 7.2.1 Basic Structure                                       | 90 |

|    |       | 7.2.2 GCC/Pin                                               | 91 |

|    |       | 7.2.3 LLVM                                                  | 92 |

|    | 7.3   | Experimental Results                                        | 92 |

| 8  | Con   | clusions                                                    | 96 |

| Bi | bliog | raphy                                                       | 98 |

# Chapter 1 Introduction

Loops account for most of the execution time in programs and thus extensive research has been dedicated to parallelize loop iterations [1, 26, 45]. Unfortunately, in many cases these efforts are hindered when the compiler cannot prove that a loop is free of *loop-carried* dependences. However, sometimes when static analysis concludes that a loop has a *may* dependence — for example when the analysis cannot resolve a potential alias relation — the dependence may actually not exist or it may occur in very few executions of the program [5, 62]. *Thread-Level Speculation* (TLS) is a promising technique that can be used to enable the parallel execution of loop iterations in the presence of *may* loop-carried dependences.

Recently hardware support for speculation has been implemented in commodity offthe-shelf microprocessors [28, 29]. However, the speculation support in these architectures was designed with *Hardware Transactional Memory* (HTM) in mind and not TLS. The only implementation of hardware support for TLS to date is in the IBM Blue Gene/Q (BG/Q), but BG/Q is not a commodity machine and thus not readily available for experimentation or usage. HTM extensions, available in the Intel Core and in the IBM POWER8 architectures, allow for the speculative execution of atomic program regions [29, 67, 28, 36]. Such HTM extensions enable the implementation of three key features required by TLS: (a) conflict detection; (b) speculative storage; and (c) transaction roll-back.

Similar to HTM, TLS employs an optimistic approach to parallelism. TLS assumes that the iterations of a loop can be executed in parallel — even in the presence of potential dependences — and then relies on a mechanism to detect dependence violations and correct them. The main distinction between TLS and HTM is that in TLS speculative transactions must commit in order, a required feature when parallelizing the execution of a loop so that loop-carried dependences from one iteration transaction to another are respected. However, among all hardware implementations that support speculation, only the IBM BG/Q supports in-order transaction commit, as it was initially designed to enable TLS [23].

Until now, the majority of the attempts to estimate the performance benefits of TLS were based on simulation studies [54, 56, 55, 47]. Unfortunately, studies of TLS execution based on simulation have serious limitations. Some interesting research questions are: (1) can the existing speculation support in commodity processors, originally designed for HTM, be used to support TLS and reduce its overhead to execute loop code? and (2) if it

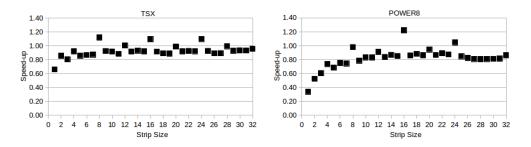

can, what performance effects would be observed from such implementations? This thesis has a cautiously positive answer to the first question, i.e. supporting TLS on top of HTM hardware is possible. To address the second question, this work presents an in-depth evaluation of the implementation of TLS on top of the HTM extensions available in the Intel Core and in the IBM POWER8 that leads to new techniques to support TLS over HTM and to some surprising discoveries about the interaction between prefetching, false sharing, and the relevance of loop characterization to predict the potential performance of TLS. The experimental results indicate that: (1) false sharing is a very important performance-hindering effect in both architectures; (2) strip mining is an effective transformation to eliminate false sharing; (3) the selected size of the strip can be critical; (4) in some cases the strip size needed to eliminate false sharing may lead to aborts because the speculative capacity of the HTM is exceeded; (5) small loops are not amenable to be parallelized with TLS on the existing HTM hardware because of the expensive overhead of: (a) starting and finishing transactions, (b) aborting a transaction, and (c) setting up loop for TLS execution; (6) loops with potential to be successfully parallelized in both Intel Core and IBM POWER8 architectures have better performance on the POWER8 because TLS can take advantage of the ability of this architecture to suspend and resume transactions to implement ordered transactions; (7) the larger storage capacity for speculative state in Intel TSX can be crucial for loops that execute many read and write operations; and (8) the ability to suspend/resume a transaction is important for loops that execute for a longer time because their transactions may abort due to OS context switching.

This work also proposes Speculative Trace Optimization (STO) to speculatively optimize and execute multiple alternative *traces* of a single iteration of a hot loop. The goal is to simultaneously execute speculative traces in hot loops to uncover hidden optimizations that could not be carried out at compile time because of program-flow indeterminism. STO is not a loop parallelization technique, rather it is a technique that speeds up both sequential and parallelizable loops. The discussion in this work focuses on the exhaustive execution of inner-loop traces, but STO can be used in other code regions and it can also be used to selectively execute a subset of speculative traces. Contrary to whole-procedure traces, the number of inner-loop traces is reasonably small, making them good candidates for speculation in current HTM architectures that have limited capacity to store speculative state [29, 30, 28, 23]. In an initial exploration that applied STO to the hot inner-loops from a set of programs, we found that at most four traces were present.

The use of STO described in this work enumerates all possible traces, optimizes them, and executes each trace speculatively in a *transaction*, using a fork/join paradigm. All conditionals that select a specific trace are evaluated at the end of each transaction to determine if the trace should commit or abort. For each loop iteration, a single trace commits while the others miss-speculate and thus should be aborted. The initial assessment of STO presented in this work uses the prototype based on TSX and applies it to benchmarks from Mediabench, Parboil and SPEC2006 benchmarks. The results reveal speed-ups of up to 9% for four cores. This initial result is encouraging given that TSX lacks multi-versioning and lazy-conflict resolution, and it has a significant abort overhead [50]. To compensate for the missing features, extra code is inserted into the original program leading to additional overhead. Achieving speed-ups even in the presence of such overheads suggests that if an HTM architecture were to incorporate such features, significant speed-ups could emerge.

On the other hand, tools to support programming correctness are central in any programming model, particularly in parallel programming, in which bugs are typically very hard to detect and reproduce [66]. A fairly common source of bugs in OpenMP and many other parallel programming models shows up when programmers need to evaluate if loops can have their iterations parallelized. In order to do so, programmers have to perform a careful and complex evaluation of the dependence of the loop-body variables across iterations. If such dependences are not present, loops are called DOALL, and its iterations can be easily parallelized. Otherwise, they are called DOACROSS loops, which are harder to parallelize and to extract good speed-ups [66]. Given that loop-bodies can have complex nested function calls, and pointer aliasing, dynamic cross-iteration dependences can occur at runtime, making the work of the programmer much harder and error prone. Complex loop-bodies can easily produce intricate runtime dependences which cannot be easily detected by the typical programmer at compile time. For this reason, effectively detecting dynamic loop cross-iteration violations is a relevant tool to support parallel programming.

In this work, we also present *parallel for check* (*check*), a new construct to OpenMP, which enables the seamless integration of loop dynamic data dependence verification in OpenMP. This construct makes possible the detection of loop-carried dependences at runtime in OpenMP programs, thus helping programmers to identify potential violations resulting from hard to detect loop-carried dependences. *check* was implemented in Pin/GCC-OpenMP and LLVM/Clang-OpenMP.

This thesis makes four main contributions. First, it shows that false sharing is an important cause of performance loss in TLS on commercial HTMs and it improves the implementation of TLS using HTM through code transformations. Second, it proposes a classification of loops based on TLS performance and doing so provides guidance to developers as to what loop characteristics make them amenable to the use of TLS on the Intel Core or on the IBM POWER8 architectures. Third, it presents a novel technique to optimize and speculate exhaustive traces, called STO, that uses HTM (specifically TSX in the prototype) to execute these traces in transactions using a fork/join paradigm. STO does not parallelize loops, rather it accelerates the sequential execution of loops: and it identifies the main features that an HTM mechanism should have to enable STO. Fourth, it presents a novel OpenMP parallel for check construct, also named check or checker, which enables the dynamic detection of loop-carried dependences. It does onthe-fly dynamic loop-carried dependence analysis of multithreaded applications, making it possible to measure the probability of loop-carried dependences (% lc) and to detect patterns of loop-carried dependences which can not be detected by means of serial or per-thread analysis, as in [69, 33, 32, 31].

The remainder of this thesis is organized as follows. Chapter 2 describes the relevant aspects of our work. Chapter 3 details the related work. Chapter 4 explains the limitations of HTM to support TLS and discusses performance limitations caused by false sharing, capacity limitations and non-consecutive array accesses. Chapter 5 describes an in-depth evaluation of TLS on HTM. Chapter 6 presents Speculative Trace Optimization (STO) and describes a prototype implemented on HTM. Chapter 7 motivates and describes the implementation of *checker*. Finally, Chapter 8 concludes the work.

Some of the material used in this thesis has been published or submitted for publication in the following papers:

- Juan Salamanca, José Nelson Amaral, and Guido Araújo. Using Hardware-Transactional-Memory Support to Implement Thread-Level Speculation. *Paper submitted to IEEE Transactions on Parallel and Distributed Systems (TPDS)*

- Juan Salamanca, José Nelson Amaral, and Guido Araújo. Performance Evaluation of Thread-Level Speculation in Off-the-Shelf Hardware Transactional Memories. Paper submitted to International European Conference on Parallel and Distributed Computing (EURO-PAR) 2017

- Juan Salamanca, José Nelson Amaral, and Guido Araújo. Evaluating and Improving Thread-Level Speculation in Hardware Transactional Memories. In IEEE International Parallel and Distributed Processing Symposium (IPDPS) 2016, May 23-27, 2016, Chicago, IL, USA

- Juan Salamanca, José Nelson Amaral, and Guido Araújo. Using Hardware Transactional Memory to Enable Speculative Trace Optimization. In International Symposium on Computer Architecture and High Performance Computing Workshop (SBAC-PADW) 2015, October 18-21, 2015, Florianopolis, Brazil

- Juan Salamanca, Luis Mattos, and Guido Araújo. Loop-Carried Dependence Verification in OpenMP. In International Workshop on OpenMP (IWOMP) 2014, September 28-30, 2014, Salvador, Brazil

# Chapter 2 Background

This chapter describes the background to introduce our work. It describes the main concepts used in Transactional Memory, Thread-Level Speculation, and Speculative Trace Optimization.

#### 2.1 Transactional Memory

Transactional memory (TM) was proposed as architectural support to make lock-free synchronization as efficient as conventional parallelization approaches based on mutual exclusion [25]. TM simplifies parallel programming by enabling a mechanism to ensure the consistency of shared data. Transactional memory systems must provide transaction *atomicity* and *isolation*, which require the implementation of the following mechanisms: *data versioning management, conflict detection*, and *conflict resolution* [37, 59].

In Transactional Memory, version management decides where new (speculative) and old data are stored. Conflict detection determines whether two operations executed in separate transactions cause a conflict, *i.e.* if they access a common memory location and at least one of the operations is a write. Conflict detection can be eager (detection is done immediately when the conflict occurs) or lazy (detection is done when transactions attempt to commit) [37]. A conflict causes at least one of the transactions involved in the conflict to abort and it may re-execute. Other actions could also be carried out to support a conflict-resolution policy. Resolution can happen eagerly when the conflict occurs or lazily when the transaction attempts to commit.

TMs can be supported in hardware (HTM) [25] and software (STM) [52]. HTM systems have lower overheads because conflict detection is done in hardware but they have lower speculative-state storage capacity and may support fewer active transactions [41]. HTMs are also easier to use because programmers only need to specify the start and the end of a transaction [65]. STM systems can have a large overhead because conflict detection is performed in software. On the other hand STMs have the advantage that they can be executed on any available hardware, and in principle have no limit on the amount of speculative state that a transaction may use.

Hybrid Transactional Memory (HyTM) is a approach to implement TM in software so that it can use best-effort HTM to boost performance but it does not depend on

| Processor type                                 | Intel Core i7-4770 | IBM POWER8    |

|------------------------------------------------|--------------------|---------------|

| Conflict-detection<br>granularity (cache line) | 64 B               | 128 B         |

| Tx Load Capacity                               | $4 \mathrm{MB}$    | 8  KB         |

| Tx Store Capacity                              | 22  KB             | 8  KB         |

| L1 Data Cache                                  | 32 KB, 8-way       | 64  KB        |

| L2 Data Cache                                  | 256  KB            | 512 KB, 8-way |

| SMT level                                      | 2                  | 8             |

Table 2.1: HTM implementations of Intel Core and IBM POWER [41].

| Table 2.2: HTM Architectural Feature | es. |

|--------------------------------------|-----|

|--------------------------------------|-----|

| Features                           | TLS          | Intel Core   | $\mathbf{P8}$ |

|------------------------------------|--------------|--------------|---------------|

| Eager Conflict Detection           | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Speculative Storage                | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Ordered Transactions               | $\checkmark$ |              |               |

| <b>Rollback Transactions</b>       | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Multi-versioned caches             | $\checkmark$ |              |               |

| <b>Resolution Conflict Policy</b>  | $\checkmark$ |              |               |

| $\mathbf{Suspend}/\mathbf{Resume}$ |              |              | $\checkmark$  |

| Lazy Conflict Detection            |              |              |               |

| Data Forwarding                    | $\checkmark$ |              |               |

| Word Conflict Detection            | $\checkmark$ |              |               |

HTM. This approach exploits HTM if it is available to achieve hardware performance for transactions that do not exceed the HTM's limitations [17].

#### 2.2 Intel Core and IBM POWER8

This section reviews HTM extensions, such as those found in Intel Core and IBM POWER8, and and the features to enable TLS.

Intel's Transactional Synchronization Extensions (TSX) provides an instruction-set interface to specify transactional execution [29] with two software interfaces: Hardware Lock Elision (HLE) and Restricted Transactional Memory (RTM). The RTM is an instructionset extension that includes the instructions xbegin, xend, and xabort. When a transaction aborts, the state of the program immediately before the xbegin instruction is recovered, all speculatively written data are dismissed, and the values stored in registers are rolled back to their values prior to the transaction. The execution restarts at a program point specified by the address given as argument to the xbegin instruction. Data written transactionally are not visible to other transactions until the transaction commits by executing the xend instruction.

POWER8 provides the first implementation of HTM that is supported directly by the POWER ISA. The main difference from POWER8 with respect to Intel TSX is its ability of pausing transactions. In POWER8, through the use of suspend regions, transactions can survive interrupts and can access memory non-transactionally while the transaction is still active. Suspended regions were designed to support debugging. While in a suspended state the thread can load memory locations accessed within the transaction and store their value into memory locations that are not included in the transaction footprint. POWER8's *Rollback-Only Transactions* (ROTs) allow store buffering without the detection of data conflicts. ROTs support single-thread speculative optimization techniques such as Trace Scheduling [36, 41].

Both Intel and IBM architectures provide instructions to begin and end a transaction, and to force a transaction to abort. To perform such operations Intel Core's *Transactional Synchronization Extensions* (TSX) implements RTM that includes **xbegin**, **xend**, and **xabort**. The corresponding instructions in the POWER8 are tbegin, tend, and tabort.

All data conflicts are detected at the granularity of the cache line size because both processors use cache mechanisms — based on physical addresses — and the cache coherence protocol to track transactional states. Aborts may be caused by: memory access conflicts, capacity issues due to excessively large transactional read/write sets or overflow, conflicts due to false sharing, and OS and micro-architecture events that cause aborts (*e.g.* system calls, interrupts or traps) [41, 67].

In both architectures, when a transaction aborts, the execution of the thread is rolled back to the point immediately before the transaction's begin instruction. An abort handler then determines if the transaction should retry or if a fall-back code should be executed. Data written transactionally are not visible to other transactions until the transaction commits by executing the end instruction. Table 2.1 summarizes the features of both architectures.

The main differences between POWER8 and the Intel Core HTMs are: (1) transaction capacity; (2) conflict granularity; and (3) ability to suspend/resume a transaction. The maximum amount of data that can be accessed by a transaction in the Intel Core is much larger than in the POWER8. This speculative storage capacity is limited by the resources needed both to store read and write sets, and to buffer transactional stores.

In POWER8 the execution of a transaction can be paused through the use of suspended regions — implemented with two new instructions: tsuspend and tresume. Using this mechanism, a transaction can survive interrupts and the thread can access memory non-transactionally while the transaction is suspended. The tsuspend instruction causes the thread to enter a suspended state where all memory accesses are non-transactional but are monitored. If any such access conflicts with the suspended-transaction working set, that transaction will abort due to a conflict after resuming (tresume). While in a suspended state the thread can load memory locations accessed within the transaction and store their values into memory locations that are not included in the transaction footprint. Thus, suspended regions also allow transactions to communicate with global flags without failing due to conflicts. This mechanism enables the implementation of an *ordered-transaction* feature in TLS [36].

#### 2.3 Thread-Level Speculation

Torrellas defines Thread-Level Speculation (TLS) as an environment where execution threads operate speculatively, performing potentially unsafe operations, and temporarily buffering the state that they generate in a buffer [60]. Then, the operations of a thread are declared to be correct or incorrect. If they are correct, the thread commits; if they are

```

for (i = 0; i < N; i++){

1

/* Start sequential segment 1 */ /* Global scalar, glob */

2

if (cond)

3

glob++;

4

else

glob=i;

6

/* End sequential segment 1 */

7

A[i]= glob*i;

8

/* Start sequential segment 2 */

9

for(j = 0; j < factor; j++){</pre>

/* Global array, B */

int tmp = B[factor*(i%4) + j];

12

tmp += i*5;

13

if(tmp\%2 == 0){

14

B[factor*(i\%4) + j] = tmp;

}

16

}

17

/* End sequential segment 2 */

18

}

19

```

Figure 2.1: A loop with two may loop-carried dependences. Adapted from [40].

incorrect, the thread is rolled back and typically restarted from its beginning. The term TLS is most often associated to a scenario where the goal is to parallelize a sequential application. However, in general, TLS can be applied to any environment where speculative threads are executed and can be squashed and restarted [60].

TLS has been widely studied [54, 56, 55]. Proposed TLS hardware systems must support four primary features: (a) data conflict detection; (b) speculative storage; (c) ordered transactions; and (d) rollback when a conflict is detected. Some of these features are also supported by the HTM systems found in the Intel Core and the POWER8, and thus these architectures have the potential to be used to implement TLS. Table 2.2 shows the necessary and advanced features required to enable TLS on top of an HTM-supporting mechanism, and its availability in some modern architectures. Neither Intel TSX nor the IBM POWER8 provide all the hardware features necessary to carry out TLS effectively.

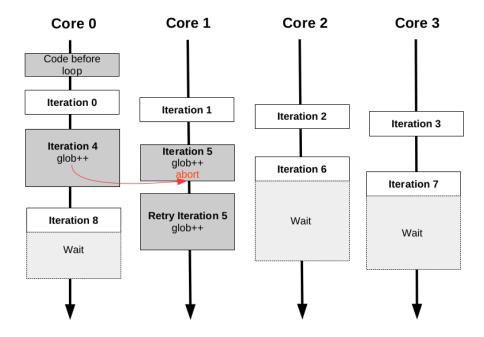

Lets examine how TLS can be applied to a simplified version of the loop example of Figure 2.1 (statement in line 8 and the inner loop are omitted) when it runs on top of an ideal HTM system containing: (a) ordered transactions in hardware; (b) multiversioning cache; (c) eager-conflict detection; and (d) conflict-resolution policy. Figure 2.2 shows the loop after it was strip-mined and parallelized for TLS using NUM\_THREADS threads. Assume that the END instruction implements: (a) ordered transactions, i.e., a transaction executing an iteration of the loop has to wait until all transactions executing older iterations have committed, and (b) a conflict-resolution policy that gives preference to the transaction that is executing the earliest iteration of the loop while rolling back later iterations. Multi-versioning allows for the removal of Write-After-Write (WAW) and Write-After-Read (WAR) loop-carried dependences on the glob variable. As shown in Figure 2.3, in the first four iterations cond evaluates false and write variable glob without aborts. Then, at iteration 4, the eager-conflict detection mechanism detects the RAW loop-carried dependence violation on variable glob between iterations 4 and 5, thus

```

d= STRIP_SIZE;

1

inc=(NUM_THREADS-1)*STRIP_SIZE;

2

i=param->i; // initial value of i for this thread

3

4

for(; i < N; i += inc ){</pre>

5

prev_i=i;

6

Retry:

7

if (!BEGIN()){

8

for (; i-prev_i < d && i < N; i++){</pre>

9

if(cond) glob++; else glob=i;

}

11

END();

12

}

else goto Retry;

14

}

15

```

Figure 2.2: Code of each thread to parallelize Figure 2.1's loop with TLS on ideal HTM system.

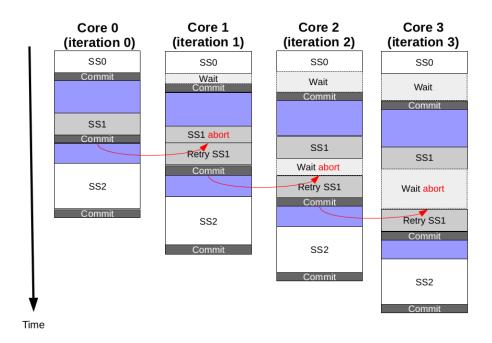

Figure 2.3: Execution flow of Figure 2.2's code with STRIP\_SIZE=1 and NUM\_THREADS=4.

rolling back iteration 5 because it should occur after iteration 4. Subsequent iterations wait for the previous iterations to commit.

#### 2.4 Strip Mining

Strip Mining divides a single loop into a pair of loops (doubly-nested loop), thus the original loop is divided into strips of some size, the *strip size*. The outer loop steps between the strips and the inner loop steps through each strip. The maximum trip count of the inner loop is equal to the strip size [66].

#### 2.5 Loop Peeling

Loop Peeling removes the first or last few iterations from a loop and performs them outside of the loop [66]. If the trip count of the loop is not constant the peeled code has to be protected with additional runtime tests.

#### 2.6 Traces

A trace is formed by basic blocks and corresponds to a cycle-free path in a control flow graph. Part of this work focuses on generating traces for hot code regions. Such regions consist of relatively few instructions that are responsible for a large share of the program execution time. Traces are good candidates for optimization [20]. In this work, hot code regions are identified using program profilers (*e.g.* VTune [49]) and then appropriate traces for STO are found within the regions.

#### 2.7 Optimizations using Traces

Generating larger traces creates more optimization opportunities because traces:

- Simplify the control-flow graph of a hot region of code such as a loop body. In STO control-flow statements are evaluated at the end of the execution of a trace and thus longer sections of control-flow free code are exposed to the compiler. The resulting control-flow graph is simpler and therefore more amenable to optimizations (dead-code elimination, code motion, constant propagation, *etc.*). This idea of optimization is used in this work.

- May contain function calls, thus incrementing the possibilities of optimization. Therefore *inlining* can be used to reduce the overhead of invoking and returning from methods [8]. This idea of optimization is also used in this work.

- Typically contain the most frequently executed portions of a program and therefore can be used to optimize frequently executed instructions [9].

- Can be used to eliminate the cost of infrequently executed instructions from the execution of hot traces [9].

## Chapter 3

## **Related Work**

This chapter presents several works that have been proposed in the literature related to Thread-Level Speculation, Speculative Trace Optimization, and Data Dependence Profiling.

#### 3.1 Thread-Level Speculation

Steffan *et al.* explored the potential of using *Thread-Level Data Speculation (TLDS)*. TLDS is a technique that allows the compiler to safely parallelize codes in cases it cannot statically prove that dependences do not exist [55]. TLDS can offer performance improvements for applications where automatic parallelization would otherwise appear infeasible.

Steffan *et al.* presented a cache coherence that supports thread-level speculation (TLS) on a wide range of different parallel architectures because it is a straightforward extension of write-back invalidation-based cache coherence [56, 57].

The absence of hardware support for TLS led to the development of software-based implementations of TLS [43, 48]. While these implementations attempt to make the best use of existing hardware resources, the large overhead of buffering, validation, and inorder commits results in degradation of performance. Thus, hardware support appears to be essential to deliver effective performance improvement with TLS.

Although much previous research work on hardware support for TLS exists, up to now (circa 2016) most attempts to estimate the performance benefits of TLS were based on simulation studies [54, 56, 55, 47]. For example, Packirisamy *et al.* show that some of the SPEC CPU 2006 benchmarks have potentially parallel loops that can be successfully parallelized with TLS to achieve up to 78% of speed-up [47]. They also predict that parallelizing loops with infrequent RAW loop-carried dependences with TLS can result in speed-ups of up to 60%. Their performance predictions are based on a trace-driven simulator based on SimpleScalar that supports multiple cores, speculative execution, and advanced TLS features. In contrast, this work describes an evaluation of TLS running on existing HTMs from both the Intel Core and the IBM POWER8. While their study assumed the absence of false sharing and the availability of multi-version caches, ordered transactions and forwarding, this work targets actual off-the-shelf HTM hardware where

none of these assumptions are true. Moreover, this work also proposes code transformations to overcome limitations of actual commercial hardware, making them amenable for efficient TLS execution.

Odaira and Nakaike study Thread-Level Speculation in the Intel TSX [44] by manually modifying parallel benchmarks from the SPEC CPU 2006 suite. Their performance evaluation indicated that up to 11% of speed-up can be achieved even without using the advanced features of HTM. However, for many benchmarks they find that TLS results in degraded performance. Their research suggests that the main reason for the performance degradation are transaction aborts due to memory conflicts. Therefore, they suggest that future HTM hardware should support not only ordered transactions but also data forwarding, multi-versioning cache, and word-level conflict detection. However, the comparison of TLS performance on Intel Core and IBM POWER8 presented in this work demonstrates that speed-ups can be achieved for some loops even on off-the-shelf hardware that does not implement their recommendations.

Nakaike *et al.* compare four HTM systems: Blue Gene/Q, zEC12, Intel TSX, and POWER8 [41]. Their experimental results indicate that the four HTM systems have implementation issues, and none has the best performance in all of the benchmarks. They claim that Intel TSX has extra transaction aborts due to adjacent cache-line prefetcher — which is corroborated by the results in this study, and that POWER8 has more capacity aborts than the other HTM systems because of its small transaction capacity — another result that is confirmed by this study. They also claim that tsuspend/tresume instructions improve TLS performance and support this claim with evaluation of two benchmarks: milc and sphinx3. They do not show the abort ratios for these two cases. In contrast, this study claims that false sharing is considerably exacerbated in TLS parallelization on top of HTM, and that although HTM features (*e.g.* suspend/resume instructions) can provide support for TLS, they do not provide all the support that is required for TLS to deliver on its promised performance.

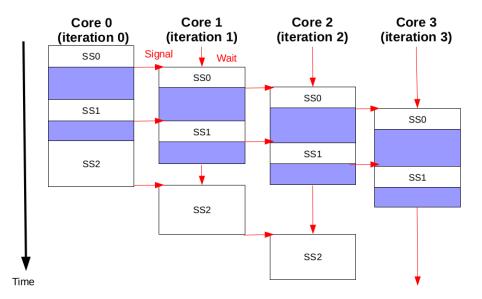

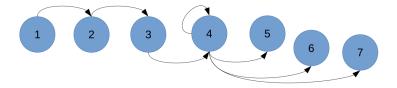

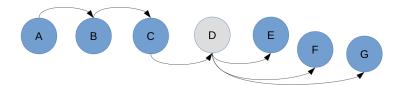

### 3.2 Speculative Execution of Loops with Transient Dependences

HELIX is a compiler that has previously delivered good speed-ups for irregular programs on a six-core Intel i7 [29] machine [11]. HELIX parallelizes loops in sequential programs, distributing the iterations to available cores in a round-robin fashion. To preserve dependences between iterations or (may) loop-carried dependences, HELIX creates *sequential segments* that are subsets of iterations whose execution on cores must respect the loop-iteration order of the sequential program. These sequential segments correspond to *Strongly Connected Components (SCCs)* in a *Data-Dependence Graph (DDG)* that have at least one loop-carried dependence. An SCC formed by a single node with no loopcarried dependences is considered a *parallel segment* that does not need synchronization. A sequential segment implements the necessary synchronization to wait for the production of a loop-carried dependence variable value from a previous iteration, and to signal when the value is ready to use in a future iteration.

Figure 3.1: HELIX Execution flow of Figure 2.1. Sequential segments are synchronized.

To understand the HELIX approach, consider the code shown in Figure 2.1. This code contains a loop where the increment of a global scalar variable glob is controlled by the condition cond. The inner loop for in lines 10- 17 reads and conditionally updates a position from array B. HELIX creates three sequential segments: Sequential Segment 0 (SS0), also called *prologue*, is always created to control the end of the loop; Sequential Segment 1 (SS1) preserves dependences in global variable glob because HELIX pessimistically assumes that cond always evaluates true; and Sequential segment 2 (SS2) surrounds the inner loop to preserve a possible dependence in some index in the array A. Figure 3.1 shows the execution of sequential segments. Static analysis cannot prove that the loop is free of loop-carried dependences, thus it must be conservative and create these sequential segments. If these dependences actually occur at runtime but they are transient, HELIX could use TLS to avoid synchronization in those sequential segments as proposed in [40].

For instance, assume an execution of the loop of Figure 2.1 that uses an input that leads to the following dependences: SS0 never has a loop-carried dependence (the value of N is known at compile time); SS1 always contains a dependence because cond always evaluates true; and SS2 contains a transient dependence. Due to this transient dependence, HELIX must synchronize SS2 and thus will not exploit parallelism in it. However, the index factor\*(i%4) + j evaluates to different values at each iteration of the outer loop if the number of cores is less than or equal to four — assuming that the distribution of iterations to cores follows a round-robin fashion.

Murphy et al. [40] propose a technique to speculatively parallelize loops that exhibit transient loop-carried dependences — a loop where only a small subset of loop iterations have actual loop-carried dependences. The code produced by their technique uses a TM hardware (TCC hardware) and software (Tiny STM) model running on top of the HELIX time emulator. They developed three approaches to predict the performance of implementing TLS on the HELIX time emulator: coarse-grained, fine-grained, and judicious. The coarse-grained approach speculates a whole iteration while the fine-grained approach speculates sequential segments and executes parallel segments without speculation. The *judicious approach* uses profile data at compile time to choose which sequential segment to speculate or synchronize so as to satisfy (may) loop-carried dependences. They conclude that TLS is not only advantageous to overcome limitations of the compiler static data-dependence analysis, but that performance might also be improved by focusing on the transient nature of dependences.

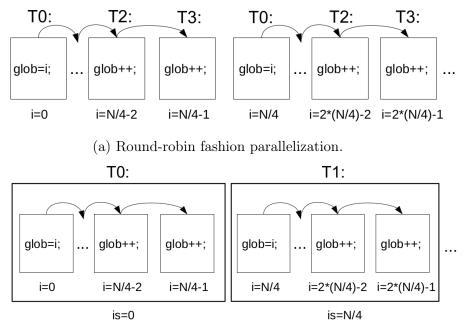

Murphy *et al.* evaluated TLS on emulated HTM hardware using **cBench** programs [15] and, surprisingly, predicted up to 15 times performance improvements with 16 cores [40]. They arose at these predictions even though they did not use strip mining to decrease the overhead of starting and finishing transactions as we suggest in this work. Particularly, fine-grained speculation without strip mining can result in large overheads due to multiple transactions (sequential segments) per iteration, even larger than coarse-grained speculation. They parallelized loops in a round-robin fashion which can result in small transactions, large number of transactions, high abort ratio, bad use of memory locality, and false sharing.

Their over-optimistic predictions are explained by the fact that their emulation study does not take into account the overhead of setting TLS up — which is specially high without strip mining. For instance, their emulation study predicted speed-ups even for small loops. However, when executing such loops in real hardware, the TLS overhead — setup, begin/end transactions, and aborts — would nullify any gain from parallel execution. In [40] the authors conclude that fine-grained speculation coupled with static dependence analysis is possibly the best way to exploit all the parallelism in loops. However, static dependence analysis can be very imprecise and report a large number of sequential segments that would prevent good speed-ups.

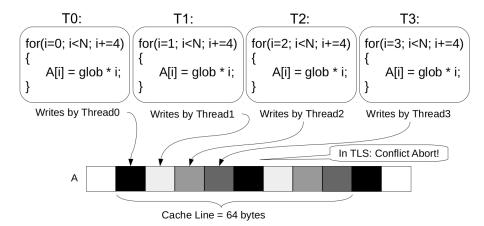

Odaira and Nakaike and Murphy *et al.* use coarse-grained TLS to speculate a (stripmined) whole iteration and perform conflict detection and resolution at the end of the iteration to detect RAW dependence violations [44, 40]. To illustrate, assume an execution of the example of Figure 2.1 where **cond** always evaluates true, and thus the **glob** variable is increased at each iteration of the outer loop. With coarse-grained TLS the execution of this outer loop would be serialized for such execution. The advantages of coarsegrained TLS are: (a) it is simple to implement because it does not need an accurate data dependence analyzer. (b) the number of transactions is smaller than or equal to the fine-grained or judicious approaches; and (c) there is no synchronization in the middle of an iteration. The downside is that even a single frequent actual loop-carried dependence will cause transactions to abort and re-execute the whole iteration, thus serializing the execution.

#### 3.3 Speculative Trace Optimization

Traces have been used for traditional optimizations. Fisher was the first to introduce the concept of traces and to use it for instruction scheduling [20]. *Trace Scheduling* is a global compaction technique in contrast with local compaction techniques whose domain is a basic block of code. The idea is to schedule the most frequently executed traces (defined

by a feedback) quickly. Extra instructions, referred as *compensation code*, must be added so that other paths not optimized by the technique become valid. This work has been extended by Ellis in the Bulldog Compiler [19], Chang *et al.* [12], and Hwu *et al.* [27].

Hwu *et al.* developed a set of techniques for exploiting ILP across basic block boundaries [27]. These techniques are based on a structure called the *superblock*. A superblock is a trace that has no side entrances, thus the control may only enter from the top but may leave at one or more exit points. A copy of a portion of a trace is made from the first side entrance to the end, and all side entrances into the trace are moved to the corresponding copy. The superblock enables the optimizer and scheduler to extract more ILP along important execution paths by removing constraints due to other unimportant execution paths.

Chang *et al.* used profiling information in the Trace Selection Algorithm (the first pass of Trace Scheduling) [12]. They examined the predictability of branches within traces, concluding the use profiling information in Trace Scheduling can guide global code motion effectively with very small off-trace overhead.

Hank *et al.* introduced a technique called *region-based compilation* where the compiler is allowed to divide the program into regions of code (instead of methods) as a desirable unit of work [22]. Region-based compilation allows the compiler to control the problem size while exposing inter-procedural optimization and code motion opportunities.

Static Trace Scheduling involves selecting traces and scheduling instructions on these traces trying to increase ILP, and improving the performance on a single processor. STO differs from these approaches because it collects all traces and speculatively optimizes and executes them on an HTM system trying to improve the performance on multiple processors.

Profile information is used to identify heavily executed paths in a program (or traces). Ball and Larus described an algorithm for path profiling that determines how many times each acyclic path in a routine executes [4]. The algorithm selects and places profile instrumentation to minimize run-time overhead, and it accurately determines dynamic execution frequency of control-flow paths in a routine. This type of profiling subsumes the basic block and edge profiling that do not always correctly predict frequencies of overlapping paths. They select a number of paths and encode them so that each path has an index that can be used to access the counter of the corresponding path.

Young developed a technique to collect path profiles efficiently, and then applies the path profile to two optimizations: static correlated branch and path-based superblock scheduling [68]. The potential next paths for a given path are kept track. At runtime, the program uses this information to find what path is being followed by at a given instruction.

Data-flow analysis computes its solution over all paths of the program; however, programs execute a small fraction of all possible paths, this subset is called *hot paths*. Ammons *et al.* described an approach to analyzing and optimizing programs, which improves the precision of data-flow analysis throughout hot paths [2]. Their technique detects hot paths, creating a *hot path graph (HPG)* where these paths are isolated. They then perform flow analysis in the original CFG and the HPG, taking a subset of the HPG that contains hot paths for which the analysis differed in a favorable way from that in the CFG. This final subset is used to perform constant propagation. Our work differs from these approaches on path profiling as they developed techniques to improve the performance of profiling, thus to use this more accurate profile information in optimizations. We profile the entire program to find the frequently executed sections of a program and then collect the traces of these sections to be speculatively executed.

Bradel *et al.* proposed and evaluated an approach for automatic parallelization based on traces as units of parallel work [7]. They described an execution model that uses traces to extract parallelism from programs. They implemented a system that shows the benefits and addresses the challenges of using traces for data-parallel programs in an off-line feedback-directed system. The results of performance compares favorably to the performance of these programs manually parallelized. Bradel *et al.* propose and evaluate an approach for automatic parallelization based on traces as units of parallel work [7]. They implement a system that takes a sequential program (binary file), identifies the traces on it, and groups them into coarse-grain units of computation (tasks). STO differs from this approach in that it uses a real HTM to speculatively optimize traces of loop iterations and we are not automatically parallelizing traces of the binary file.

Neelakantam *et al.* proposed that microprocessors provide hardware primitives for atomic execution to increase the effectiveness of speculative compiler optimizations [42]. Thus, the compiler may speculatively optimize a program's hot path in isolation as a superblock. Atomic execution guarantees that if a miss-speculation is produced, the control is transferred to a non-speculative version of the code, relieving the compiler from generating compensation code. They considered that the implementation of the proposed hardware atomicity has significant differences from TM. These optimizations result in 10-15% average speed-up. STO differs from this in that, to carry out the speculative compiler optimizations, it speculates in parallel all possible traces within a hot-loop iteration using a real HTM.

#### 3.4 Data-Dependence Profilers

This section analyzes two techniques used to detect loop-carried dependences. The first one is the *Pairwise* method, which was used in [35]; the second technique is the *Stride-based* method, which was implemented in the  $SD^3$  profiler [33, 32].

Static dependence analysis techniques have been extensively studied in the literature. Approaches like the GCD Test [39] and Banerjee's equality test [34] have been used, for a long time, in the design of parallelizing compilers. These techniques analyze data dependences in array-based memory accesses, and thus are not effective when used in languages which allow pointers and dynamic allocation. Besides, static analysis can become complex in situations when: (a) the bounds of the loop are not known, (b) dynamically created arrays are passed through deep procedure call chains, or (c) the loop-body has a complicated control-flow. In such cases, dynamic loop dependence analysis is an alternative as all memory addresses are resolved at runtime.

#### 3.4.1 Pairwise Method

The Pairwise Method is still considered the state-of-the-art for loop-carried dependence testing. The basic idea of this method is to store, into a hash table (*pending table*), all memory references (*pending references*) occurring during the current iteration of a loop. When an iteration finishes, the pending table is compared against the *history table*, which stores all memory references (*history references*) of all previous iterations. This method solves nested loops dependences, by having a pending and a history table for each loop.

The Pairwise algorithm works as follows. First, memory references are stored into the pending table during an iteration. After of finishing the iteration, the pending table is checked against the history table to discover loop-carried dependences. Before of continuing with the next iteration, the pending references are copied to the history. This process is repeated until the end of all iterations for this loop. If this loop is nested within another loop, the history table of the inner loop is propagated to the pending table of the outer loop. Afterwards, this pending table is checked against the history table of the outer loop (that is initialized empty) to discover loop-carried dependences. This process for the outer loop continues until the end of all its iterations.

Loop-independent dependence does not prevent parallelization; thus, any dependence analyzer must distinguish if a dependence is loop-carried or loop-independent. The Pairwise algorithm, as described in [33, 69], detects loop-independent dependence by implementing *kill addresses* (a technique similar to the notion of *kill sets* in *data-flow analysis*), which marks a memory address as killed once it is written in an iteration. Then all memory references within the same iteration to the killed address are ignored. However, this technique could lead to incorrect results in multithreaded program executions not reporting existing violations of loop-carried dependences between threads as it only works in serial executions or per-thread analysis.

To demonstrate *kill addresses* effectiveness,  $SD^3$  authors analyze the following code from SPEC 179.art [33].

```

void match() {

1

if (condition)

2

pass_flag=1;

3

}

4

void scan_recognize(...) {

for (j = starty; j < endy; j += stride)</pre>

6