#### **University of Alberta**

#### **Library Release Form**

Name of Author: Johnny Huynh

Title of Thesis: Minimizing Address-Computation Overhead

**Degree**: Master of Science

**Year this Degree Granted**: 2006

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

Johnny Huynh Department of Computing Science, University of Alberta, Edmonton, Alberta, Canada

| Da | ıte <sup>.</sup> |  |  |

|----|------------------|--|--|

|    |                  |  |  |

Debugging is twice as hard as writing the code in the first place. Therefore, if you write the code as cleverly as possible, you are, by definition, not smart enough to debug it.

- Brian W. Kernighan

#### **University of Alberta**

| MINIMIZING        | ADDRESS- | -COMPUTATION | OVERHEAD |

|-------------------|----------|--------------|----------|

| IVITINTIVITZITNUT | ADDRESS- | COMPUTATION  | OVERHEAL |

by

#### Johnny Huynh

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**.

in

Department of Computing Science

Edmonton, Alberta Fall 2006

## **University of Alberta**

### **Faculty of Graduate Studies and Research**

| nate Studies and Research for accep | re read, and recommend to the Faculty of Grad-<br>tance, a thesis entitled <b>Minimizing Address</b> -<br>by Johnny Huynh in partial fulfillment of the<br>er of Science. |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     |                                                                                                                                                                           |

|                                     |                                                                                                                                                                           |

|                                     |                                                                                                                                                                           |

|                                     |                                                                                                                                                                           |

|                                     |                                                                                                                                                                           |

|                                     | José Nelson Amaral                                                                                                                                                        |

|                                     |                                                                                                                                                                           |

|                                     | Vincent Gaudet                                                                                                                                                            |

|                                     |                                                                                                                                                                           |

|                                     | M.H. (Mike) MacGregor                                                                                                                                                     |

|                                     |                                                                                                                                                                           |

Date: \_\_\_\_\_

## **Abstract**

In many digital signal processors (DSPs), variables stored in memory are accessed using address registers and indirect addressing modes. The addressing code used to access these variables can have a significant impact on code size and performance. Thus, one optimization problem DSP compilers face is the problem of minimizing address-computation overhead. This thesis identifies three problems that must be addressed in order to minimize overhead: access-sequence generation, offset assignment, and address-code generation. Although these three problems have been extensively studied individually by other researchers, this work examines all three problems simultaneously to understand how each problem affects the overhead of the final code. Specifically, we propose a Minimum-Cost Flow (MCF) model to generate optimal addressing code for a *fixed* access sequence and memory layout. In order to minimize address-computation overhead, we must find an access sequence and memory layout that generates an MCF model that has minimum overhead.

By exhaustively evaluating the solution space of five small DSP benchmarks, the results of this thesis suggest that the access-sequence generated has very little impact on address-computation overhead, while the offset assignment of variables has a significant impact. We show that current offset-assignment heuristics proposed in the literature [15, 18, 23, 29] do not adequately address the offset assignment problem. In order for these algorithms to produce an offset assignment with minimal overhead, a new combinatorial problem, the *Memory Layout Permutation* problem, must be addressed. Alternatively, offset assignment algorithms can be designed to produce an MCF model that produces low overhead. This thesis presents and evaluates three such algorithms. We observe that each algorithm has an impractical running-time or does not consistently generate low-overhead memory layouts.

## Acknowledgements

First and foremost, I would like to thank my supervisor, Dr. José Nelson Amaral, for making this thesis possible. His advice and guidance during my undergraduate and graduate studies have been invaluable in my academic and personal development.

Next, I would like to thank two colleagues, Dr. Sid-Ahmed-Ali Touati and Paul Berube, for their assistance and feedback throughout this research project. Their knowledge and insight of the problem models and DSP architecture were instrumental in the identification and formalization of the problems presented in this thesis.

Last, but certainly not least, I would like to give my deepest thanks and appreciation to my family. I am grateful that both, my brother, Andrew, and my fiancée, Jennifer, are computer scientists who understand the time and effort I needed to dedicate to this research. To my parents, Tho and Suong, I cannot express enough gratitude for their love and support through the years.

## **Table of Contents**

| 1 |      | oduction 1                               |

|---|------|------------------------------------------|

|   | 1.1  | Processor Model                          |

|   | 1.2  | Methods to Reduce Overhead               |

|   |      | 1.2.1 Offset Assignment                  |

|   |      | 1.2.2 Access-Sequence Generation 6       |

|   |      | 1.2.3 Address-Code Generation            |

|   | 1.3  | Motivating Example                       |

|   | 1.4  | Contributions                            |

| 2 | Rela | ited Work 14                             |

| _ | 2.1  | Simple Offset Assignment                 |

|   | 2.2  | Address-Register Assignment              |

|   | 2.3  | Generating Access Sequences              |

|   | 2.4  | Generating Access Sequences              |

|   | ∠,¬  | 2.4.1 Minimum-Cost Circulation           |

|   |      | 2.4.2 Minimum-Weight Perfect Matching    |

| _ |      |                                          |

| 3 |      | ending Current Models 24                 |

|   | 3.1  | Memory-Layout Permutations               |

|   | 3.2  | Minimum-Cost Flow                        |

|   |      | 3.2.1 Impact of Removing Redundant Edges |

|   | 3.3  | Conflict General Offset Assignment       |

|   | 3.4  | Summary                                  |

| 4 | Und  | erstanding the Solution Space 39         |

|   | 4.1  | Experimental Methodology                 |

|   | 4.2  | Experimental Methodology                 |

|   | 4.3  | Instruction-Scheduling Solution Space    |

|   | 4.4  | Features                                 |

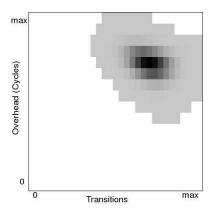

|   |      | 4.4.1 Transition Count                   |

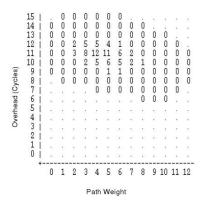

|   |      | 4.4.2 Path Weight                        |

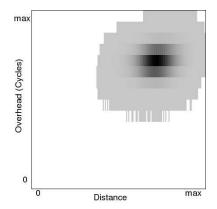

|   |      | 4.4.3 Distance Measurement               |

|   |      | 4.4.4 Interleavings                      |

|   |      | 4.4.5 Live Ranges                        |

|   |      | 4.4.6 Conflicts                          |

|   |      | 4.4.7 Evaluating Features                |

|   | 4.5  | Summary                                  |

| 5  | Eval   | luating Offset Assignment Algorithms | <b>59</b> |

|----|--------|--------------------------------------|-----------|

|    | 5.1    | Experimental Methodology             | 60        |

|    | 5.2    |                                      | 60        |

|    | 5.3    | Efficiency of ARA Algorithms         | 62        |

|    | 5.4    | Efficiency of SOA Algorithms         | 66        |

|    | 5.5    | Summary                              | 66        |

| 6  | Eval   | luating Alternative Algorithms       | 70        |

|    | 6.1    | Best-First Search                    | 70        |

|    | 6.2    |                                      | 75        |

|    | 6.3    |                                      | 76        |

|    |        | 6.3.1 Variable Access Patterns       | 77        |

|    |        | 6.3.2 Augmented Interference Graph   | 78        |

|    |        |                                      | 82        |

|    | 6.4    | Efficiency of Alternative Algorithms | 87        |

| 7  | Con    | clusions                             | 90        |

|    | 7.1    | Future Work                          | 93        |

| Bi | bliogr | aphy                                 | 94        |

# **List of Figures**

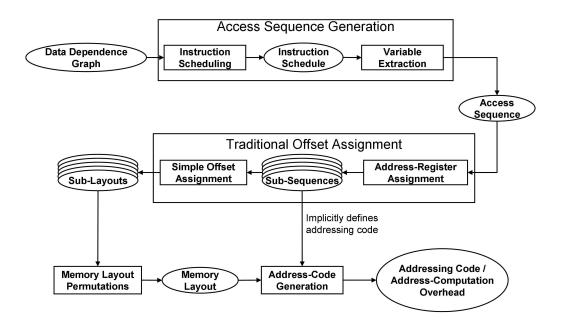

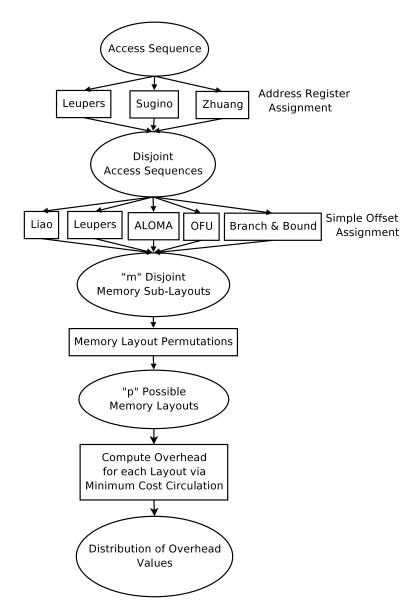

| 1.1        | The processes involved in minimizing address-computation overhead. Traditionally, assumptions made during offset assignment implicitly define the final memory layout and addressing code       | 5        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | A three-address instruction can be converted into three different se-                                                                                                                           |          |

| 1.3        | ries of machine instructions                                                                                                                                                                    | 8        |

| 1.4        | Instructions for address registers $A_1$ and $A_2$ , using the layouts in Figures 1.3(a) and 1.3(b)                                                                                             | 10       |

| 1.5        | Accessing the variables in Layout 1.3(c) requires 5 cycles of overhead.                                                                                                                         | 10       |

| 1.6        | Accessing the variables in Layout 1.3(d) requires 6 cycles of overhead.                                                                                                                         | 11       |

| 1.7        | Layout 1.3(e) is optimal as the variables can be accessed with the minimum amount of overhead — 4 cycles                                                                                        | 11       |

| 2.1        | The relationship between access-sequence generation and offset assignment.                                                                                                                      | 19       |

| 3.1        | Performing address register assignment followed by simple offset assignment generates memory sub-layouts that must be placed in memory. The problem of finding a placement that minimizes over- |          |

| 2.2        | head is called the memory layout permutations problem                                                                                                                                           | 25<br>26 |

| 3.2<br>3.3 | Permutations of two sub-layouts                                                                                                                                                                 |          |

| 3.4        | minimum-cost flow are shown                                                                                                                                                                     | 28<br>30 |

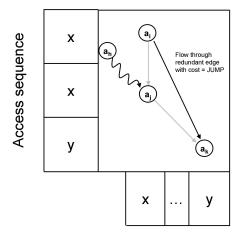

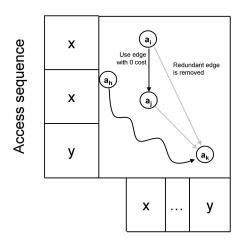

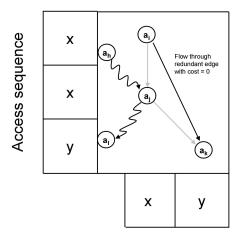

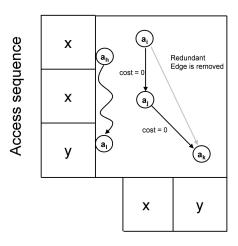

| 3.5        | Let the grey lines be edges with no flow; and black lines be edges with a unit flow. Removing a redundant edge with cost=JUMP in                                                                |          |

| 3.6        | the network-flow graph does not increase the cost of the flow Let the grey lines be edges with no flow; and black lines be edges with a unit flow. Removing a redundant edge with cost=0 in the | 31       |

| 3.7        | network-flow graph does not increase the cost of the flow The TMS320C54X family of DSPs can encode a three-operand in-                                                                          | 32       |

|            | struction in fewer machine instructions than tradition accumulator-<br>based architectures                                                                                                      | 36       |

| 4.1        | Methodology used to exhaustively evaluate the solution space                                                                                                                                    | 40       |

| 4.2        | Two memory layouts that are reciprocals of each other are considered equivalent because they have the same overhead                                                                             | 41       |

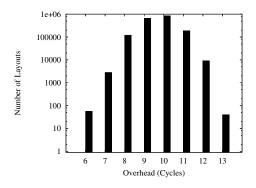

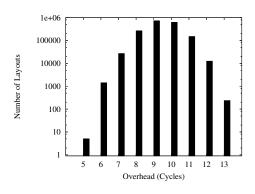

| 4.3        | Distribution of overhead values produced by three C-GOA access sequences from the latnrm_ptr kernel that can be considered undecirable.                                                         | 47       |

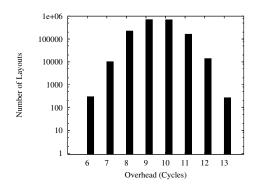

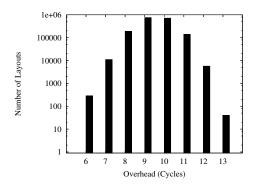

| 4.4        | sirable                                                                                                                                                                                         | 47       |

|            | sequences from the latnrm_ptr kernel that can be considered desirable.                                                                                                                          | 48       |

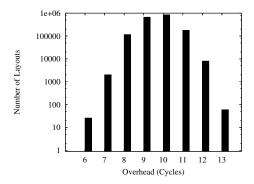

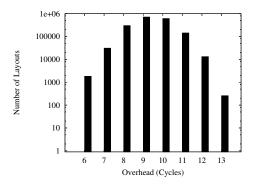

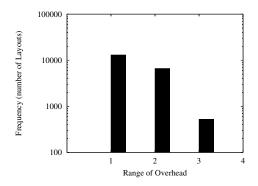

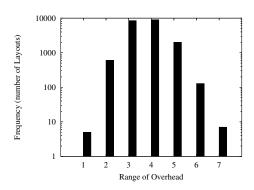

| 4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Frequency of layouts that have a specified range of possible overhead values                                                   | 50<br>57<br>57<br>57<br>57      |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.1                             | Procedure for evaluating offset assignment algorithms. There are 15 paths in the chart, for the 15 combinations of ARA and SOA |                                 |

| 5.2                             | algorithms                                                                                                                     | 61                              |

| 5.3                             | values obtained by exhaustive search                                                                                           | <ul><li>64</li><li>67</li></ul> |

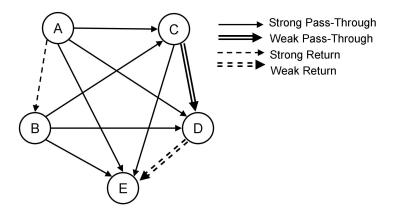

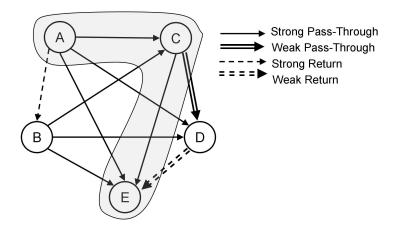

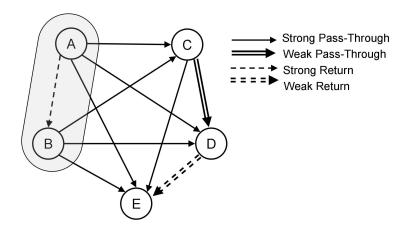

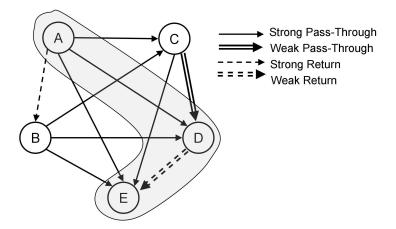

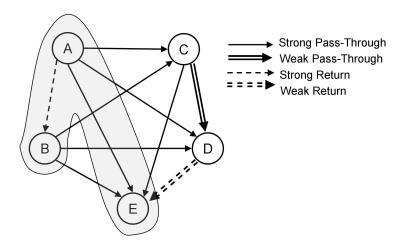

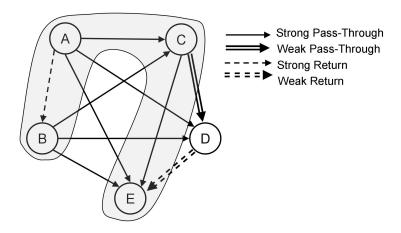

| 6.1                             | An access sequence                                                                                                             | 77                              |

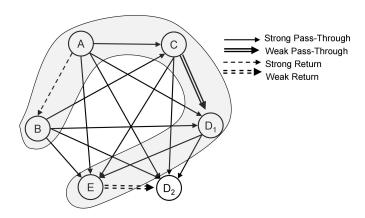

| 6.2                             | An Augmented Interference Graph (AIG) for the access sequence                                                                  | 70                              |

| 6.3                             | in Figure 6.1                                                                                                                  | 79<br>80                        |

| 6.4                             | An R-path is a directed path composed of <i>pass-through</i> edges                                                             | 80                              |

| 6.5                             | A PR-path is a directed path composed of a P-path, followed by an                                                              | 00                              |

|                                 | R-path.                                                                                                                        | 81                              |

| 6.6                             | A PR'-path is composed of a PR-path and R-path, using the same                                                                 |                                 |

|                                 | root.                                                                                                                          | 81                              |

| 6.7                             | The longest path cover found for the given AIG                                                                                 | 83                              |

| 6.8                             | An access sequence based on Figure 6.1, but with variable D split                                                              | 86                              |

| 6.9                             | into $D_1$ and $D_2$                                                                                                           | 86                              |

|                                 |                                                                                                                                |                                 |

## **List of Tables**

| 3.1        | The size of the network-flow graph, produced by different access sequences, can be significantly reduced by removing redundant edges. The impact of removing redundant edges becomes more significant as the size of the access sequence, and resulting network-flow graph, increases                                                                                                                  | 35<br>36 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2 | Size of problem and solution space for selected kernels Number of layouts with a specific address-computation overhead, for the GOA and CGOA solution spaces, for the iir_arr benchmark                                                                                                                                                                                                                | 41       |

| 4.3        | kernel                                                                                                                                                                                                                                                                                                                                                                                                 | 42       |

| 4.4        | Number of layouts with a specific address-computation overhead, for the GOA and CGOA solution spaces, for the latnrm_arr_swp                                                                                                                                                                                                                                                                           | 43       |

| 4.5        | benchmark kernel                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 4.6        | mark kernel                                                                                                                                                                                                                                                                                                                                                                                            | 44       |

| 4.7        | Scheduling statistics for two benchmark kernels                                                                                                                                                                                                                                                                                                                                                        | 46       |

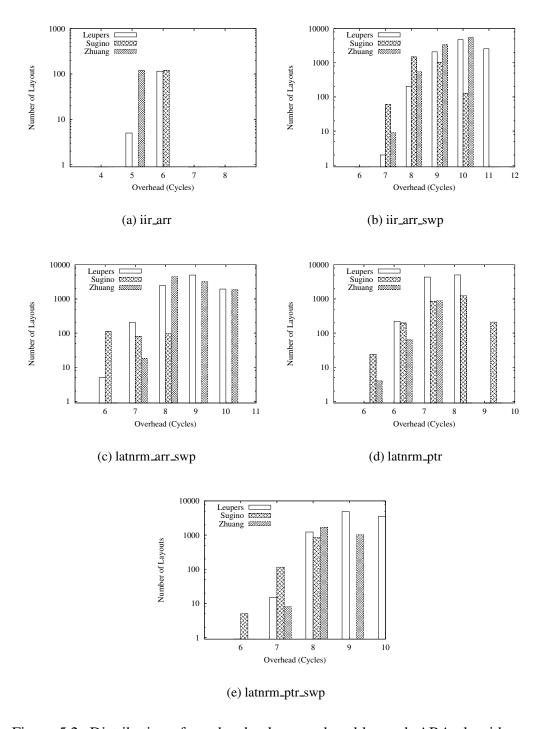

| 5.1        | Number of layouts with a specific address-computation overhead, for the entire solution space. The <i>Exhaustive</i> column shows distribution of memory layouts in the solution space. The <i>Algorithmic</i> column shows the combined distribution of layouts produced by the 15 different ARA and SOA combinations                                                                                 | 63       |

| 5.2        | Number of memory layouts produced by each ARA algorithm, with<br>the specified overhead. Each column is the combined distribution<br>of 5 sets of layouts, each produced with 5 different SOA algorithms,<br>but using the same ARA algorithm. The layouts are plotted against                                                                                                                         | 65       |

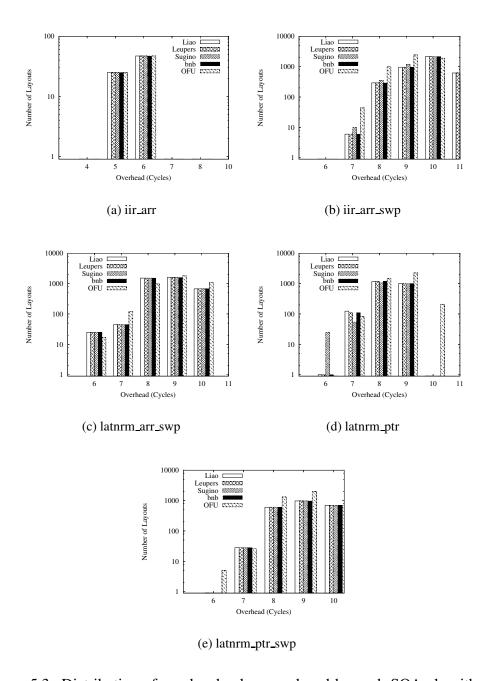

| 5.3        | the full range of overhead values obtained by exhaustive search Number of memory layouts, produced by each SOA algorithm, with the specified overhead. Each column is the combined distribution of 3 sets of layouts, each produced with 3 different ARA algorithms, but using the same SOA algorithm. The layouts are plotted against the full range of overhead values obtained by exhaustive search | 68       |

| 6.1        | Efficiency of best-first search and random search for GOA problems where the minimum overhead values are known                                                                                                                                                                                                                                                                                         | 73       |

| 6.2  | Efficiency of best-first search and random search for C-GOA prob-    |   |     |

|------|----------------------------------------------------------------------|---|-----|

|      | lems where the minimum overhead value is known                       |   | 73  |

| 6.3  | Efficiency of best-first search and random search for GOA problems   |   |     |

|      | where the minimum overhead value is not known                        |   | 74  |

| 6.4  | Efficiency of best-first search and random search for C-GOA prob-    |   |     |

|      | lems where the minimum overhead value is not known                   |   | 74  |

| 6.5  | Efficiency of the greedy algorithm for generating layouts for C-     |   |     |

|      | GOA problems                                                         |   | 76  |

| 6.6  | Efficiency of the greedy algorithm for generating layouts for GOA    |   |     |

|      | problems                                                             |   | 76  |

| 6.7  | Efficiency of the three alternative algorithms for generating a mem- |   |     |

|      | ory layout for C-GOA problem. The minimum and maximum over-          |   |     |

|      | head values are found by exhaustive evaluation of the entire offset  |   |     |

|      | assignment solution space                                            |   | 88  |

| 6.8  | Efficiency of the three alternative algorithms for generating a mem- |   |     |

|      | ory layout for GOA problems. The minimum and maximum over-           |   |     |

|      | head values are found by exhaustive evaluation of the entire offset  |   |     |

|      | assignment solution space                                            |   | 88  |

| 6.9  | Efficiency of the three alternative algorithms for generating a mem- |   |     |

| - 10 | ory layout for C-GOA problems                                        | • | 89  |

| 6.10 | Efficiency of the three alternative algorithms for generating a mem- |   | 0.0 |

|      | ory layout for GOA problems                                          |   | 89  |

## **List of Acronyms**

AIG Augmented Interference Graph

AR Address Register

**ARA** Address-Register Assignment

**BFS** Best-First Search

C-GOA Conflict General Offset Assignment

**DDG** Data Dependence Graph

**DSP** Digital Signal Processor

**GOA** General Offset Assignment

MCC Minimum-Cost Circulation

MCF Minimum-Cost Flow

MLP Memory Layout Permutation

**MWPC** Minimum-Weight Path Cover

MWPM Minimum-Weight Perfect Matching

**SOA** Simple Offset Assignment

## Chapter 1

## Introduction

Digital signal processors (DSPs) are small, low-powered processors found in embedded systems, such as cell phones, portable music players, and cameras. DSPs are designed with a minimal number of functional units and instructions to keep processor size and power consumption minimal, while maintaining enough functionality to meet a specific application, such as processing audio and video data. A common design for these processors is an accumulator-based, register-memory architecture, where instructions can use data in memory without explicitly loading the data into a general purpose register. Instead of storing data in general-purpose registers, the addresses to data are stored in special registers called *address registers* (ARs) and accessed through several different addressing modes. The architectural advantages of address registers is that they only need to be large enough to hold addresses, and can be manipulated using simplified arithmetic units called address-generation units.

DSPs that are commonly used to process audio and video data must efficiently access large arrays of data in memory. To facilitate the memory accesses, post-increment and post-decrement indirect addressing modes are available in many DSPs. These addressing modes allow the processor to access a word in memory, specified by the address in an AR, and then modify the address in the AR by one word without additional instructions or processor cycles. When two consecutive memory accesses indexed by the same address register are to non-adjacent words in memory, an extra address-computation instruction is required. This extra instruction increases code size and introduces additional latency in the program. In this

thesis, *overhead* refers to the extra processor cycles required to perform address computations. Thus, the placement of data in memory, and the order in which the data is accessed, affects how often the post-increment or post-decrement addressing modes can be used.

Another architectural feature present in some DSPs to assist in address computations is a *modify register*. DSPs with modify registers can increment or decrement the address in an address register by the amount specified in a modify register without additional overhead. That is, an address register can be post-incremented (or post-decremented) without overhead by more than one word if the appropriate value exists in a modify register.

The overhead incurred by inefficient usage of address registers, modify registers, and addressing modes is called *address-computation overhead*. Specifically, there are two specific address-computation overhead — *initialization* and *jump*. Initialization overhead is incurred when an immediate value is initially loaded into an AR, usually requiring a double-word instruction. Jump overhead is incurred when an explicit address-computation is required for an AR to access two non-adjacent words in memory. The introduction of double-word instructions and additional single-word instructions has several undesirable consequences:

- code size increases;

- address-computations have non-zero latency, possibly reducing performance;

- more processor resources are used, increasing power consumption.

In this thesis, initialization and jump overheads are parameterized by INIT and JUMP cycles of latency, respectively.

#### 1.1 Processor Model

The processor modeled in this thesis is based on the Texas Instruments TMS320C54X family of processors [24]. These DSPs have 8 16-bit address registers. Most instructions are 1 word in length and have 1 cycle of overhead. Initializing an address register requires a double-word instruction and has 2 cycles of latency. Instructions

may use a post-increment (or post-decrement) addressing mode to change the value of an address register by one word without additional overhead. Post-incrementing (or post-decrementing) an address register by more than one word requires an additional word to encode the explicit address-computation and results in an extra cycle of latency to execute the instruction. Thus, INIT=2 cycles and JUMP=1 cycle of overhead.

In the TMS320C54X family of processors, one address register  $AR_0$  can be used as a modify register. This capability introduces two problems for deciding how to best use  $AR_0$ . If  $AR_0$  is used as an address register, then all eight address registers can only be post-incremented (or post-decremented) by one word without overhead. If  $AR_0$  is used as a modify register, then only seven address registers are available for indirect addressing, and the compiler must determine a modify value to store in  $AR_0$ . For this work, modify register optimizations are not considered, and  $AR_0$  is only used as an address register in the processor model.

Similar to many other DSP architectures, the address registers in the TMS320C54X family of processors can also be used to store values other than addresses; however, the values stored in the address registers are subject to two limitations:

- 1. Address registers can only hold 16-bit values, while data in memory and the accumulator are 32-bit and 40-bit values respectively.

- 2. Address registers can only be manipulated by the address-generation unit, which is limited to addition and subtraction of 16-bit values.

Thus, address registers cannot be used as general purpose registers, and the problem of minimizing address computation overheads remains a relevant problem in relatively modern processors such as the TMS320C54X family of DSPs.

#### 1.2 Methods to Reduce Overhead

Given a basic block of code, there are several optimization opportunities to reduce address-computation overhead: access-sequence generation, offset assignment, and address-code generation. Figure 1.1 illustrates the processes involved in minimizing

overhead. First, an access sequence must be generated to define the order in which memory locations are accessed. Next, offset assignment is performed in two phases: address register assignment (ARA) produces sub-sequences of accesses, and simple offset assignment (SOA) produces a memory layout for each sub-sequence. After a memory layout has been defined, the final addressing code can be generated.

Traditional approaches to minimizing overhead only focus on generating access sequences and memory sub-layouts. In previous research, the problem of permuting sub-layouts to form a single memory layout does not exist; and address-code generation is implicitly defined by address-register assignment. In this thesis, the offset assignment problem is extended to explicitly consider the memory layout permutation problem, and the problem of minimizing overhead is examined as a combination of three problems: offset assignment, access-sequence generation, and address-code generation.

The problem of minimizing overhead, and its associated sub-problems, are *optimization* problems; however, the problems can also be easily cast as *decision* problems. Thus, the complexity of the optimization problems discussed in this thesis will be classified using complexity classes such as P and NP [5].

#### 1.2.1 Offset Assignment

Minimizing address-computation overhead is most often done by addressing the offset-assignment problem. Given a set of variables stored contiguously in memory, a *memory layout* is an ordering of these variables in memory. The order of variable accesses by the instructions in a basic block defines an *access sequence*. The *Offset-Assignment Problem* is defined as:

Given k address registers and a basic block accessing n variables, find a *memory layout* that minimizes address-computation overhead.

Memory layouts with minimum overhead are called optimal memory layouts. This problem is called "offset assignment" because the address of each variable can be obtained by adding an *offset* to a common base address. If k = 1, then the problem is know as the *Simple Offset Assignment* (SOA). If k > 1 the problem is referred to

Figure 1.1: The processes involved in minimizing address-computation overhead. Traditionally, assumptions made during offset assignment implicitly define the final memory layout and addressing code.

as the General Offset Assignment (GOA).

In the Simple Offset-Assignment (SOA) problem, a single AR is available to access all the variables in the memory. Liao *et al.* convert the access sequence to an undirected *access graph* [18]. Variables are vertices in the graph, and edge weights indicate the number of times two variables are adjacent in the access sequence. Liao *et al.* show that the SOA problem can be reduced, in polynomial time, to the problem of finding a maximum-weight path cover in the access graph. Finding a maximum-weight path cover is an NP-complete problem; thus, the SOA problem is also NP-complete [5]. Approximation algorithms for the SOA problem are presented in Section 2.1.

In the General Offset-Assignment (GOA) problem, each access to one of the n variables in an access sequence must be assigned to one of k address registers. This assignment creates multiple access sub-sequences — one for each address register. A memory sub-layout can be found for each sub-sequence. Sub-layouts cannot be computed independently because a variable may appear in multiple address registers, but the union of all sub-layouts must still form a contiguous layout. Liao  $et\ al$ .

simplify the GOA problem by assigning *variables*, instead of *variable accesses*, to address registers [18]. This simplification produces sub-sequences that access disjoint sets of variables. A sub-layout can be obtained by solving the SOA problem for each sub-sequence, and the resulting set of sub-layouts can form a single memory layout. In this thesis, the problem of assigning *variables* to address registers is called the *Address-Register Assignment* (ARA) problem, and the problem of forming a single memory layout from a set of disjoint sub-layouts is called the *Memory Layout Permutations* (MLP) problem. Approximation algorithms for the ARA problem are discussed in Section 2.2. The MLP problem has not been addressed in the literature because each sub-layout is traditionally assumed to be independently accessed in memory. The formulation of the MLP problem is presented in Section 3.1.

#### 1.2.2 Access-Sequence Generation

Since instance of the offset assignment problem is defined by the input access sequence, changing the access sequence can potentially change the final overhead of a given basic block of code. Generating an access sequence can be separated into two separate processes: instruction scheduling and variable extraction. Previously proposed algorithms that attempt to optimize the two processes are discussed in Section 2.3.

The first process involved in generating an access sequence is instruction scheduling. Let G=(V,E) be a directed graph where each vertex in V represents an instruction using three-address code. Each edge  $(u,v)\in E$  represents a scheduling dependency where instruction u must be scheduled before instruction v. Thus, G is a data dependence graph (DDG) that defines a partial ordering of instructions, whereas a schedule s is a fully-ordered list of instructions that also satisfies the partial ordering specified by G. Let S be the set of all legal schedules of G. GOA(s) represents the overhead of the optimal memory layout for a schedule  $s \in S$ .

An instruction schedule for a basic block defines a sequence of three-address codes but does not necessarily define an access sequence. Variable extraction is required to identify the order in which variables in memory are accessed, thereby

defining an access sequence. Figure 1.2.2 shows how a single three-operand instruction can produce three different instruction sequences, and consequently, three different access sequences. Each variable in the instruction shown in Figure 1.2(a) represents a variable that must be stored, and accessed, in memory. In an accumulatorbased machine, the instruction would typically be translated to a series of instructions as shown in Figure 1.2(b). The first source operand y is loaded, followed by a load of the second the source operand z. The newly computed result is then stored into the target operand x. Thus, the resulting access sequence is 'y z x'. If the operator used in the instruction is commutative (such as addition), then the first two accesses in the sequence can be reversed so that the second source operand in the instruction is accessed before the first operand, as shown in Figure 1.2(c). Another optimization that can affect the access sequence is variable coalescing. Variable coalescing identifies a set of variables that can be assigned to a single memory location. In particular, if one variable is defined after the last use of another variable, the values of the two variables can safely be stored in the same memory location. For example, if z is never accessed after the instruction in Figure 1.2(a), then the variables z and x can be coalesced into one memory location, and represented by one variable w. The resultant machine instructions as shown in Figure 1.2(d), with an access sequence of 'y w w'. Thus, variable coalescing changes the access sequence by reducing the number of unique variables accessed.

This thesis does not consider the optimization opportunities related to variable extraction. Thus, in the scope of this research, a schedule defines a unique access sequence. Additionally, the problem of generating an access sequence that ultimately results in a minimum overhead can then be defined. The problem of finding a minimum-overhead access sequence is to find a schedule  $s \in S|GOA(s)| \le GOA(s'), \forall s' \in S$ .

#### 1.2.3 Address-Code Generation

After an instruction schedule and memory layout have been formed, addressing code must be generated. Addressing code dictates which variable *accesses* are to be addressed by each address register, and ultimately determines the address-

$$x = y + z$$

$$ACC = y$$

$$ACC += z$$

$$x = ACC$$

(a) A three-operand instruction.

(b) Machine instructions for an accumulator-based processor.

$$ACC = z$$

$ACC = y$

$ACC += y$   $ACC += w$

$x = ACC$   $w = ACC$

(c) An alternative series of machine instructions.

(d) If z is never used after the instruction, z and x can be coalesced into w.

Figure 1.2: A three-address instruction can be converted into three different series of machine instructions.

computation overhead for a basic block. Notice that the address-register assignment phase during offset assignment implicitly defines addressing code, and subsequently, the address-computation overhead value. However, address-register assignment can produce sub-optimal addressing code because it assigns *variables*, instead of accesses, to address registers. Instead of producing addressing-code based on address-register assignment, optimal address-code generation algorithms can be used. An assignment of accesses to address registers that produces the minimum overhead can be found in polynomial-time using the algorithms presented in Section 2.4. The existence of these algorithms creates a potentially large disparity between the overhead values modeled in traditional offset assignment and the actual overhead incurred by using optimal address-code generation.

### 1.3 Motivating Example

Using the processor model described in Section 1.1, consider a basic block of code that accesses 6 variables in memory. For illustrative purposes, assume the following fixed access sequence: 'a d b e c f b e c f a d'. The traditional approach to minimize overhead is to perform offset assignment by partitioning the variables into disjoint sets. Each set is accessed exclusively by a single address reg-

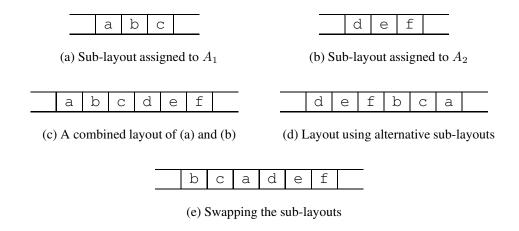

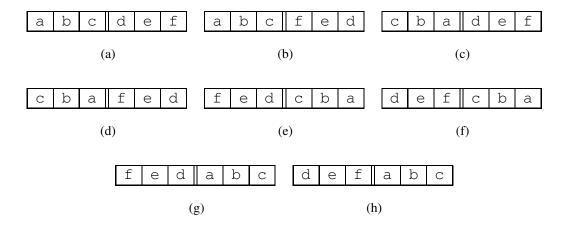

Figure 1.3: Several memory layouts.

ister. For example, variables  $\{a,b,c\}$  can be assigned to address register  $A_1$ , and variables  $\{d,e,f\}$  to address register  $A_2$ . The variables assigned to each address register can then be independently arranged in memory to form two independent *sub-layouts*, as shown in Figure 1.3. Address registers  $A_1$  and  $A_2$  independently access the variables, as shown in Figures 1.4(a) and 1.4(b). In this example, the address register assigned to each layout must each perform one initialization and one explicit address computation. Thus, the overhead for each address register is 3 cycles, for a total of 6 cycles of overhead.

In the traditional approach to the GOA problem, the sub-layouts in Figure 1.3 are considered "optimal" for two reasons. First, no ordering exists for either variable subset, {a,b,c} or {d,e,f}, with less than 3 cycles of overhead. Second, no partitioning of the 6 variables exists that can produce sub-layouts with a total overhead that is less than 6 cycles. Do these sub-layouts minimize the overhead of the input access sequence? No. The problem is the restriction that each set of variables be accessed by a single address register.

The memory layouts in Figures 1.3(a) and 1.3(b) can be placed contiguously in memory to form the single memory layout shown in Figure 1.3(c). Figure 1.5 shows that  $A_1$  can be used for the last access of variable d (originally assigned to  $A_2$ ) without requiring additional overhead. Similarly,  $A_2$  is used for the last access of variable a (originally assigned to  $A_1$ ). This solution has an overhead of 5 cycles instead of 6.

| variable |        | addressing  |          |

|----------|--------|-------------|----------|

| accessed | offset | code        | overhead |

|          |        | $A_1 = \&a$ | 2        |

| a        | 0      | $A_1 += 1$  |          |

| b        | 1      | $A_1 += 1$  |          |

| С        | 2      | $A_1 = 1$   |          |

| b        | 1      | $A_1 += 1$  |          |

| С        | 2      | $A_1$ -= 2  | 1        |

| a        | 0      | $A_1$       |          |

(a) Instructions for address register  $\mathcal{A}_1$

| variable |        | addressing  |          |

|----------|--------|-------------|----------|

| accessed | offset | code        | overhead |

|          |        | $A_2 = \&d$ | 2        |

| d        | 0      | $A_2 += 1$  |          |

| е        | 1      | $A_2$ += 1  |          |

| f        | 2      | $A_2 = 1$   |          |

| е        | 1      | $A_2$ += 1  |          |

| f        | 2      | $A_2$ -= 2  | 1        |

| d        | 0      | $A_2$       |          |

(b) Instructions for address register  $A_2$

Figure 1.4: Instructions for address registers  $A_1$  and  $A_2$ , using the layouts in Figures 1.3(a) and 1.3(b)

| variable |        | addressing  |          |

|----------|--------|-------------|----------|

| accessed | offset | code        | overhead |

|          |        | $A_1 = \&a$ | 2        |

|          |        | $A_2 = \&d$ | 2        |

| a        | 0      | $A_1 += 1$  |          |

| d        | 3      | $A_2$ += 1  |          |

| b        | 1      | $A_1 += 1$  |          |

| е        | 4      | $A_2$ += 1  |          |

| С        | 2      | $A_1 = 1$   |          |

| f        | 5      | $A_2 = 1$   |          |

| b        | 1      | $A_1 += 1$  |          |

| е        | 4      | $A_2 += 1$  |          |

| С        | 2      | $A_1 += 1$  |          |

| f        | 5      | $A_2$ -= 5  | 1        |

| a        | 0      | $A_2$       |          |

| d        | 3      | $A_1$       |          |

|          |        |             |          |

Figure 1.5: Accessing the variables in Layout 1.3(c) requires 5 cycles of overhead.

| variable |        | addressing  |          |

|----------|--------|-------------|----------|

| accessed | offset | code        | overhead |

|          |        | $A_1 = \&a$ | 2        |

|          |        | $A_2 = \&b$ | 2        |

| a        | 5      | $A_1$ -= 5  | 1        |

| d        | 0      | $A_1 += 1$  |          |

| b        | 3      | $A_2$ += 1  |          |

| е        | 1      | $A_1 += 1$  |          |

| С        | 4      | $A_2 = 1$   |          |

| f        | 2      | $A_1 = 1$   |          |

| b        | 3      | $A_2$ += 1  |          |

| е        | 1      | $A_1 += 1$  |          |

| С        | 4      | $A_2$ += 1  |          |

| f        | 2      | $A_1$       |          |

| а        | 5      | $A_2$ -= 5  | 1        |

| d        | 0      | $A_2$       |          |

Figure 1.6: Accessing the variables in Layout 1.3(d) requires 6 cycles of overhead.

| variable |        | addressing  |          |

|----------|--------|-------------|----------|

| accessed | offset | code        | overhead |

|          |        | $A_1 = \&b$ | 2        |

|          |        | $A_2 = \&a$ | 2        |

| a        | 2      | $A_2$ += 1  |          |

| d        | 3      | $A_2$ += 1  |          |

| b        | 0      | $A_1 += 1$  |          |

| е        | 4      | $A_2$ += 1  |          |

| С        | 1      | $A_1 = 1$   |          |

| f        | 5      | $A_2$ -= 1  |          |

| b        | 0      | $A_1$ += 1  |          |

| е        | 4      | $A_2$ += 1  |          |

| С        | 1      | $A_1 += 1$  |          |

| f        | 5      | $A_2$       |          |

| a        | 2      | $A_1$ += 1  |          |

| d        | 3      | $A_1$       |          |

Figure 1.7: Layout 1.3(e) is optimal as the variables can be accessed with the minimum amount of overhead — 4 cycles.

Now, consider an alternative sub-layout to 1.3(a), with the variables ordered as  $\{b,c,a\}$ . Variables  $\{d,e,f\}$  are kept in the same order as shown in Figure 1.3(d). Similar to Figure 1.4, if variables  $\{d,e,f\}$  are assigned to  $A_1$  and variables  $\{b,c,a\}$  are assigned to  $A_2$ , the total overhead is 6 cycles. If the two sub-layouts are placed contiguously in memory the minimum overhead is still 6 cycles, as shown in Figure 1.6.

However, if variables  $\{b, c, a\}$  are placed before variables  $\{d, e, f\}$ , producing the memory layout shown in Figure 1.3(e), and each variable can be accessed by more than one address register, then the address computation overhead is reduced to 4 cycles, as shown in Figure 1.7. Despite the similarities with memory layouts 1.3(c) and 1.3(d), the layout in Figure 1.3(e) is the only one that allows for the minimum amount of overhead.

Clearly, in order to minimize address-computation overhead for a basic block of code, the offset assignment problem must be solved. Unfortunately, solving the ARA and SOA problems alone is not sufficient to minimize overhead because of the restriction that each variable must be accessed by a single address register. Ultimately, address-computation overhead is dictated by the addressing code generated, which allows multiple address registers to access the same variable. Thus, if it is possible to generate optimal addressing code for a fixed access sequence and memory layout, the following questions are raised:

- Do different ARA and SOA heuristics affect the combined-layout overhead?

- How should sub-layouts be arranged to minimize address-computation costs?

- How do different access sequences (found through instruction scheduling)

affect overhead?

- What is the minimum amount of address-computation overhead required for a given basic block of code?

This thesis addresses these questions through an exhaustive exploration of the solution space.

#### 1.4 Contributions

The rest of this thesis is organized as follows. Previously proposed algorithms that affect address-computation overhead are presented in Chapter 2. The problems with previously proposed techniques are discussed in Chapter 3. Specifically, three new contributions are presented:

- the formulation of a new optimization problem, the Memory Layout Permutations problem, that has to be solved in order to minimize overhead when generating memory layouts using the traditional approach;

- an extension of the offset assignment problem, called the Conflict General Offset Assignment problem, that reflects the changes in address registers and memory in modern DSP architectures;

- a minimum-cost flow (MCF) model for the generation of addressing code for a fixed access sequence and memory layout. Let L be the number of accesses and N be the number of variables. This MCF model has at least \( \frac{L}{N} \) fewer edges than Gebotys' minimum-cost circulation (MCC) model, as demonstrated in Section 3.2.

The rest of the thesis presents several experimental results. Chapter 4 examines the solution space for access-sequence generation and offset assignment. Examining the solution spaces demonstrate that optimal address-code generation alone is not sufficient to minimize address-computation overhead. Furthermore, the offset assignment has significant impact on overhead, while access-sequence generation does not. Chapter 5 presents an empirical evaluation of heuristic-based algorithms published in the literature for offset assignment and demonstrates that these algorithms produce poor approximations to the minimization of address-computation overhead. Alternative algorithms for offset assignment are presented and evaluated in Chapter 6. Lastly, conclusions on the study and future work are discussed in Chapter 7.

## Chapter 2

## **Related Work**

This chapter presents the different approaches and algorithms that can affect address-computation overhead. As mentioned in Section 1.2, overhead is reduced by addressing three issues: offset assignment, access-sequence generation, and address-code generation. Algorithms designed to approximate solutions for the offset assignment problem are presented in Sections 2.1 and 2.2. Section 2.3 presents research that affect how access sequences are generated, and Section 2.4 presents two algorithms to generate optimal addressing-code for a fixed offset assignment and access sequence.

### 2.1 Simple Offset Assignment

Bartley introduced the SOA problem in 1992 and solved it as a maximum-weight Hamiltonian-path problem [2]. A path in the access graph represents the ordering of variables in memory. Liao  $et\ al$ . refine the problem formulation to a  $maximum-weight\ path-cover$  problem (MWPC) [18]. They improve the run-time complexity of Bartley's algorithm to approximate a solution to the SOA problem. This improved algorithm begins by marking all edges of the access graph G as f as f as f and sorts them in decreasing order of weight. The algorithm then iterates the list of removable edges and marks each edge as f as f and f are f are f are f and f are f are f and f are f are f are f and f are f are f are f and f are f are f are f are f are f and f are f are f and f are f are f are f are f are f and f are f are f and f are f and f are f are f and f are f and f are f are f are f and f are f are f and f are f are f and f are f and f are f are f are f and f are f are f and f are f and f are f are f and f are f are f and f are f are f are f and f are f and f are f are f and f are f and f are f are f and f are f and f are f are f and f are f and f are f and f are f are f and f are f are f are f and f are f are f are f and f are f are f are f are f are f and f are f and f are f are

able edges incident to e are removed. The algorithm terminates when all edges have either been removed or marked as unremovable. The unremovable edges form an approximate maximum-weight path cover.

Leupers proposes to extend Liao's algorithm by using a tie-break function to decide between edges that have equal weights [16]. This function computes the sum of the weights of incident edges to the edge being evaluated. When a tie occurs, the edge with the lowest sum is selected. Using this tie-break function usually increases the weight of path cover, resulting in memory layouts with lower address-computation overhead [16, 13].

Sugino *et al.* propose to approximate a MWPC by iteratively removing edges from the access graph using a greedy heuristic [23]. Each edge e=(u,v) in the access graph is evaluated using two metrics, the *fork* value of the endpoints u,v, and the *cycle* value of the edge e. The *fork* value of a vertex v is defined as:

$$fork(v) = \max\{degree(v) - 2, 0\}$$

The cycle value of an edge e is defined as:

$$cycle(e) = \begin{cases} 1 & \text{if } e \text{ is part of a cycle} \\ 0 & \text{otherwise} \end{cases}$$

Using these two metrics, the *benefit* of each edge e=(u,v) access graph is defined as:

$$benefit(e) = \frac{fork(u) + fork(v) + cycle(e)}{weight(e)}$$

In each iteration of the algorithm, the edge with the highest benefit is removed. The benefit of each edge is re-evaluated and the process continues until the access graph becomes a path.

For evaluation purposes (see Chapter 5), a naive and an optimal algorithm to find a memory layout for the SOA problem are also implemented. The naive algorithm produces a memory layout based on the declaration order of variables. Two variables, u and v, are adjacent in memory if and only if there are no other variables that are declared between the declaration of u and the declaration of v. The algorithm is known as the Order First Use (OFU) algorithm [13, 18]

Liao  $et\ al.$  propose an algorithm that finds an optimal layout for the SOA problem using the branch-and-bound technique [17]. The algorithm has an exponential running time but can compute the MWPC for graphs with 12 vertices in a reasonable amount of time. The algorithm is based on the observation that an access graph with n variables has n-1 edges in a maximum-weight path cover. Given a partial path cover p with m < n-1 edges, there is a set of  $valid\ edges$  that can be added to p. An edge e is valid if adding e to p does not form a cycle in p and does not cause a vertex in p to have a degree greater than two. Let p' be the partial cover p augmented with e. An upper bound on a path cover subsuming p' is the weight of p' plus the n-m heaviest valid edges. If the upper bound of p' is greater than the current maximum weight path cover, the procedure is recursively called. Otherwise, p' is discarded and another valid edge is added to p. When there are no more valid edges to add to p, the MWPC is found, producing an optimal memory layout for the SOA problem.

### 2.2 Address-Register Assignment

In the GOA problem, k > 1 address registers are used to access variables in memory. Liao *et al.* decompose the GOA problem into multiple instances of the SOA problem by assigning each variable to an address register  $A_i$ . Let  $C(A_i)$  be the address-computation overhead for an optimal SOA solution to variables assigned to  $A_i$ . Liao *et al.* define the GOA problem as follows:

Given an access sequence S, the set of variables V, and k address registers, assign each  $v \in V$  to an address register  $A_i, 1 \leq i \leq k$ , such that  $\sum_{i=1}^k C(A_i)$  is minimum.

Solving this problem does not produce a memory layout — it only produces an assignment of variables to address registers. Additionally, as shown in the example in Section 1.3, assigning variables to address registers may not necessarily minimize the overall address-computation overhead. Thus, this problem should not be considered as the *real* GOA problem. In this thesis, the problem is called the Address-Register Assignment (ARA) problem. Finding an optimal solution to the

ARA problem is NP-hard because the SOA problem, which is NP-complete, is an instance of the ARA problem [5].

Three algorithms that approximate a solution to the ARA problem are examined in this thesis. In order to approximate the minimum overhead, an approximation of  $C(A_i)$  is required. Any one of the SOA algorithms in Section 2.1 can be used as a sub-routine for the following ARA algorithms to approximate the overhead of assigning a variable to an address register.

Leupers and David propose to solve the ARA problem by using a greedy algorithm based on selecting edges [16]. Given an access graph G, the algorithm assigns the k heaviest disjoint edges of G to each address register. Each remaining variable  $v \in V$  is assigned to the address register  $A_i$  for which v causes the minimum increase to  $C(A_i)$ .

Sugino  $et\ al.$  use an heuristic-based algorithm for the ARA problem [23]. Their algorithm requires two disjoint partitions of all the variables. They claim that starting with one partition with all variables and one partition with no variables works best. Each variable is initialized as not-yet-moved. The algorithm moves one variable at a time from one partition to the other. The gain of moving a variable from  $A_i$  to  $A_j$  is the reduction of  $C(A_i) + C(A_j)$ . At each iteration, the algorithm moves the not-yet-moved variable that yields the highest gain. The algorithm saves all the intermediate partitions and their costs. When all the variables have been moved, the intermediate partition configuration that has the lowest total cost is selected. If there are k > 2 address registers available, the procedure is repeated on each pair of address registers until no movement occurs.

Zhuang et al. propose a technique to simplify offset assignment problems using variable coalescing [29]. They propose an algorithm to assign variables to address registers that is independent of the variable coalescing technique. The algorithm assigns a single variable to a single address register at a time. Each unassigned variable  $v \in V$  is added to each address register  $A_i$  and the increase in  $C(A_i)$  is computed. The assignment that results in the lowest increase is committed. If there is a tie, a weighted access graph G is used. Let weight(v, u) be the weight of the edge connecting v and u in G. Let  $(v, A_i)$  be an assignment of v to  $A_i$ . For each

$(v,A_i)$  that is tied, the following score is computed:

$$w1(v, A_i) = \sum_{u \in A_j, j \neq i} weight(v, u)$$

The assignment with the maximum w1 score is selected. This process continues until all variables are assigned to an address register.

Although many approaches to the GOA problem address the ARA and SOA problems separately, some researchers have proposed algorithms that address both problems simultaneously using iterative approaches. Atri *et al.* propose an SOA algorithm that iteratively improves a given memory layout [1]. Similarly, Wess and Zeitlhofer propose to approximate a solution to the GOA problem by iteratively modifying offset assignments and address register assignments [26]. Leupers and David propose to find a memory layout for the GOA problem using a genetic algorithm [15], while Wess and Gotschlich propose to generate memory layouts using simulated annealing [15, 27]. These algorithms are excluded from the experiments in Chapter 5 because their performance is dependent on the initial memory layout produced. Additionally, simulation-based algorithms can be run for an unspecified number of iterations, making it difficult to compare to heuristic-based algorithms.

Despite the large number of algorithms proposed by researchers to generate an offset assignment and address-register assignment, only two comprehensive comparisons of the algorithms exist. Leupers presents the *OffsetStone* benchmark suite and application to evaluate algorithms for the SOA problem [13]. Huynh *et al.* use a minimum-cost circulation technique (discussed in Section 2.4) to accurately evaluate a combination of SOA and ARA heuristic-based algorithms [8].

### 2.3 Generating Access Sequences

As mentioned in Section 1.2, instruction scheduling and variable extraction can affect the access sequence used in the offset assignment problem. Many algorithms have been proposed to improve overhead through instruction scheduling or re-ordering variable accesses. Rao and Pande apply algebraic transformations (such as commutativity) on expression trees to produce a *least-cost access sequence* [22]; Lim *et al.* manipulate the entire instruction schedule [19]. Kandemir *et al.* propose

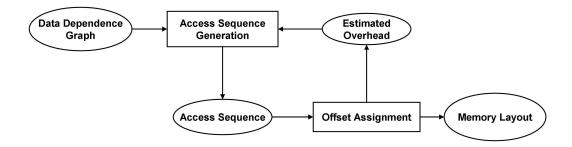

Figure 2.1: The relationship between access-sequence generation and offset assignment.

an algorithm to change the access sequence after a memory layout is formed for each basic block [9]. Unfortunately, these algorithms share two major drawbacks. First, the objective of the algorithms is to produce an access sequence that can be accessed with minimal cost by a single address register. That is, the algorithms are primarily designed to produce access sequences for the SOA problem. Second, the algorithms rely on an effective offset assignment algorithm to generate the access sequence, as shown in Figure 2.1. An offset assignment algorithm is used to determine the overhead of potential access sequences. Once an access sequence is generated, the offset assignment algorithm is invoked again to produce a memory layout. A unified algorithm for scheduling and offset assignment by Choi and Kim avoids both drawbacks. Choi and Kim observe that small changes in the instruction schedule produces localized changes in the access graph. Thus, it is possible to incrementally compute the overhead associated with each change in the access sequence. The main drawback to this technique is its iterative nature, which may not always be a feasible approach in a compiler, especially if each iteration is computationally intensive.

After an instruction schedule is found, there is another opportunity to decrease address-computation overhead through variable coalescing. Ottoni *et al.* coalesce variables and simultaneously find a memory layout for instances of the SOA problem [21]. Similarly, Zhuang *et al.* propose algorithms that coalesce variables for both SOA and GOA problems [29]. Although the coalescing algorithms in both works simultaneously find memory layouts, it is still possible to perform an addi-

tional offset assignment pass to further reduce address-computation overhead.

The majority of studies related to minimizing address-computation overhead have traditionally focused on offset assignment for *scalar* variables in *straight line code*. Few studies treat *array* accesses in *loops*. Leupers and David propose both a branch-and-bound and heuristic-based algorithm to improve AR usage for array accesses in loop bodies [14]. Cheng and Lin propose a graph-based address register allocation and data re-ordering algorithm to reduce overhead for loop execution [4]. Chen and Kandemir present a scheme to transform arrays and reschedule array accesses to reduce overhead using minimum cost traversals of reference graphs [3]. Zhang and Yang propose a procedure-level method of offset assignment that uses an access graph with information from a control-flow graph [28].

#### 2.4 Address Code Generation

After an instruction schedule and a memory layout have been found, the final addressing code must be generated. Traditionally, the address-register assignment produced during offset assignment defines the addressing code. That is, if each variable in an access sequence has already been assigned an address register to access it, then no additional work is required. However, address-register assignment during offset assignment only assigns *variables* to address registers. As depicted in Figure 1.1 and demonstrated in Section 1.3, the address-computation overhead for a basic block of code is ultimately determined by the addressing code generated. Specifically, overhead for a given access sequence and memory layout is minimized by assigning *variable accesses* to address registers. There are two known techniques to generate optimal addressing code: minimum-cost circulation and minimum-weight perfect matching.

#### 2.4.1 Minimum-Cost Circulation

An algorithm to find the optimal addressing code is proposed by Gebotys [6]. Gebotys shows that the assignment of accesses to address registers can be found in polynomial time by transforming S and M into a directed cyclic network-flow graph.

The minimum cost circulation (MCC) of the graph represents the optimal addressing code, and the cost of the circulation represents the minimum overhead for the given memory layout. The MCC for a fixed memory layout can be computed using integer linear programming where the constraint matrix is totally unimodular, and thus, can be solved in polynomial time. All memory layouts in this paper evaluate the quality of a memory layout using this technique. Gebotys' MCC technique is reproduced here for the reader's convenience.

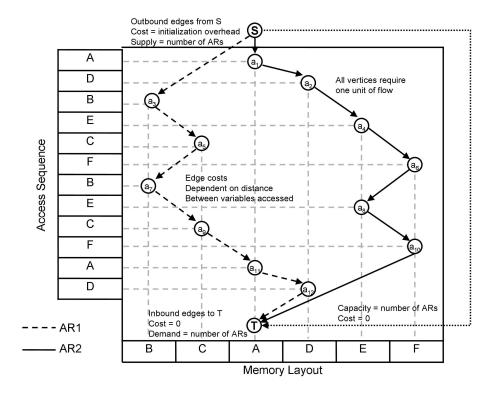

Let G=(V,E) be a network-flow graph with vertices V and edges E. V is composed of the accesses  $a_i \in S$ , and two special vertices, source  $a_s$  and sink  $a_k$ . Let  $(a_i,a_j)$  represent an access to  $a_i$ , immediately followed by an access to  $a_j$ . E is composed of directed edges  $(a_i,a_j)$ , for all  $a_i$  that are accessed before  $a_j$ . The cost,  $c_{i,j}$ , associated with each edge,  $(a_i,a_j)$ , represents the overhead for a single address register to consecutively access  $a_i$  then  $a_j$ . E also contains special edges that connect the source and sink vertices,  $(a_s,a_i)$  and  $(a_i,a_t)$ ,  $\forall a_i \in S$ . These edges do not represent actual accesses in S, thus their cost is zero. E also has a special edge connecting the sink to the source,  $(a_t,a_s)$ . Each unit-flow through this edge represents an address register initialization, thus its cost is  $c_{t,s} = INIT$ .

To find the minimum cost circulation of G, a set of linear constraints are placed on the flow through each edge in E. Let  $e_{i,j}$  represent the amount of flow through edge  $(a_i, a_j) \in E$ .

Since  $(a_t, a_s)$  represents address register initialization, the flow through this edge cannot exceed the number of available address registers, r:

$$0 \le e_{t,s} \le r$$

All other edges represent an access by a single address register, thus the flow through these edges must be non-negative and not greater than 1.

$$0 \le e_{i,j} \le 1, i \ne k, j \ne s$$

The minimum cost circulation must also satisfy the *conservation of flow* property [11], thus the total flow into a vertex must equal the total flow out of the vertex:

$$\sum_{j} e_{i,j} - \sum_{j} e_{j,k} = 0$$

Finally, the model must ensure that each access,  $a_j \in S$ , is executed exactly once. This condition can be expressed by adding a constraint on each directed edge ending at  $a_j$ .

for each

$$j \neq s,k, \sum_{i \neq j} e_{i,j} = 1$$

Thus, the minimum cost circulation of G is found by minimizing the total cost of the flows:

$$z = \sum_{e_{i,j} \in E} c_{i,j} e_{i,j}$$

subject to the constraints described above.

Since variables  $e_{i,j}$  have non-negative integer bounds, the flows through the graph are guaranteed to be integers because [6, 11]. Thus, the MCC of a given memory layout can be solved in polynomial time with a linear programming library or solver.

#### 2.4.2 Minimum-Weight Perfect Matching

An alternative technique to generate optimal addressing code is to use the minimum-weight perfect matching (MWPM) technique proposed by Udayanarayanan [25]. Given an access sequence S and a memory layout M, the MWPM technique builds a bipartite graph as follows:

Let G=(V,E) be a bipartite graph with vertices V and edges E. V is composed of pairs of vertices,  $x_i$  and  $y_i$ , representing each access  $a_i \in S$ . V also contains pairs of vertices,  $s_r$  and  $t_r$ ,  $1 \le r \le k$ , representing the k address registers. E is composed of four types of undirected edges:

- $(y_i, x_j)$ , i < j. These edges model an AR accessing  $a_i$  followed by  $a_j$ , thus the edge cost is  $c_{i,j}$ .

- ullet  $(y_i,s_r).$  These edges model an AR accessing  $a_i$  first.

- $(x_i, t_r)$ . These edges model an AR accessing  $a_i$  last.

- $(s_r, t_r)$ . These edges model unused ARs in addressing code.

The MWPM of G represents addressing code, for the given S and M, with minimum overhead. The advantage to using the minimum-weight perfect matching technique is a faster running time. Let l be the number of accesses in S. The complexity of finding a minimum-weight perfect matching is  $O((l+k)^3)$ , while the running time to find a minimum-cost circulation is  $O(l^4 \log l)$  [25]. However, since k is small and bounded, the MWPM can be found in less time.

# Chapter 3

# **Extending Current Models**

Chapter 2 clearly shows that there has been a significant amount of research on problems that involve reducing address-computation overhead; however, there are still more opportunities to further reduce overhead in DSP codes and to do so using more precise and more efficient models and algorithms. This chapter presents three improvements in current problem models in order to more accurately model the problem of minimizing address-computation overhead. Specifically, Section 3.1 presents a new problem called the *memory-layout permutation* problem that arises from the separation of offset assignment and address-code generation. In Section 3.2, an alternative model for address-code generation is proposed. The new model is based on the minimum-cost flow technique presented in Section 2.4. This new model is more efficient and easier to implement. Lastly, in Section 3.3, a new variant of the offset assignment problem is introduced to reflect advancements in modern DSP architectures.

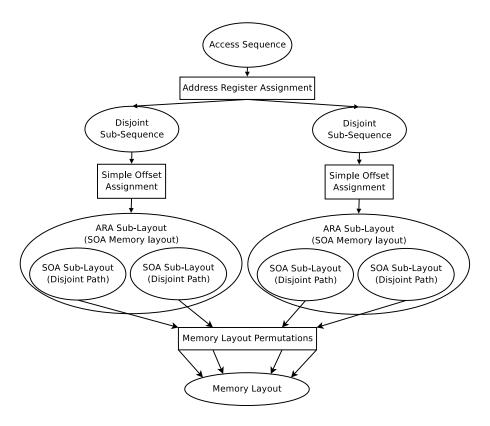

## 3.1 Memory-Layout Permutations

Figure 3.1 illustrates the traditional process of generating a memory layout. ARA produces a set of disjoint access sub-sequences that are solved as independent SOA problems. Solving each SOA instance produces a memory layout called an ARA sub-layout. Each ARA sub-layout is accessed independently through a single address register, thus, each sub-layout can be placed independently in memory. Additionally, each ARA sub-layout is a set of disjoint paths that cover an access graph

Figure 3.1: Performing address register assignment followed by simple offset assignment generates memory sub-layouts that must be placed in memory. The problem of finding a placement that minimizes overhead is called the memory layout permutations problem.

for an SOA problem. Each disjoint path is called an SOA sub-layout and defines a contiguous ordering of variables in memory. Since the SOA sub-layouts are disjoint and accessed by a single address register, it is not possible to use a post-increment (or post-decrement) addressing mode to consecutively access two variables in two different sub-layouts. Thus, SOA sub-layouts can also be placed independently in memory. Unless otherwise stated, the term *sub-layout* refers to an SOA sub-layout.

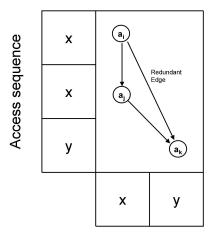

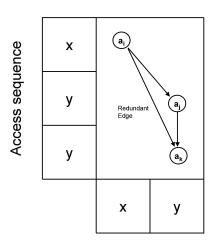

However, Section 1.3 demonstrates that if a variable can be accessed by multiple ARs, address-computation overhead may be reduced by placing the sub-layouts contiguously in memory. Since the MCC technique allows variables to be accessed by multiple ARs, the sub-layouts should no longer be placed independently in memory. Let  $M_i$  be a sub-layout and  $M_i^r$  be a sub-layout with the variables of  $M_i$  in reverse order in memory. Let  $(M_i|M_i^r)$  stand for an instance of either  $M_i$  or  $M_i^r$ . The *memory layout permutations* (MLP) problem is introduced as follows:

Figure 3.2: Permutations of two sub-layouts

Given an access sequence S and a set of m disjoint memory sublayouts, find an ordering of the sub-layouts  $\{(M_1|M_1^r),\ldots,(M_m|M_m^r)\}$  such that address-computation overhead is minimum when the sublayouts are placed contiguously in memory.

The MLP solution space is extremely large. Given m sub-layouts, there are m! permutations of sub-layouts. For each permutation, each sub-layout can be placed in memory as either  $M_i$  or  $M_i^r$ . Thus, m sub-layouts originate  $(m!)(2^m)$  layouts. However, because all variables have the same relative offset to each other, an ordering of layouts  $M_1, \ldots, M_m$  is equivalent to its reciprocal layout,  $M_m^r, \ldots, M_1^r$ , Thus, the MLP solution space is  $\frac{(m!)(2^m)}{2}$  memory layouts. Figure 3.2 shows how 2 sub-layouts can form 8 possible layouts, half of which are reciprocals of another.

When reciprocals are considered, an offset assignment problem with n variables has a solution space of  $\frac{n!}{2}$  memory layouts. In the degenerate case, each sub-layout can be a single variable, m=n, and the MLP problem is reduced to the offset assignment problem. This reduction implies that if an algorithm solves the MLP problem, the same algorithm solves the offset assignment problem.

## 3.2 Minimum-Cost Flow

Although the MCC and MWPM techniques (see Section 2.4) can generate optimal addressing code in polynomial time, it is possible to further reduce the running time

to find optimal addressing code. This thesis proposes to use a minimum-cost flow (MCF) model to generate optimal addressing code. The MCF model has two practical advantages over the MCC and MWPM techniques. First, the MCF problem is a well-known problem with many algorithms and solvers implemented, such as LEDA [20]. The experiments performed in this thesis use Goldberg's efficient implementation of a scaling algorithm [7]. Second, the proposed MCF model uses a smaller network flow graph than the MCC and MWPM models, further reducing the execution time requirements for generating optimal addressing code.

The network-flow graph used in the MCF technique is very similar to the graph used by Gebotys, and can be constructed as follows. Let G = (V, E) be a networkflow graph with vertices V and edges E. V is composed of the accesses  $a_i \in S$ , and two special vertices, source  $a_s$  and sink  $a_t$ .  $a_s$  has an excess supply equal to the number of address registers, and  $a_t$  has a demand equal to the number of address registers. All other vertices in V have a minimum and maximum flow capacity of 1. That is, each vertex must have one unit of flow through it. Let  $(a_i, a_j)$ represent an access to  $a_i$ , immediately followed by an access to  $a_i$ . E is composed of directed edges  $(a_i, a_j)$ , for all accesses  $a_i \in S$  that are accessed before access  $a_j \in S$ . The cost,  $c_{i,j}$ , associated with each edge,  $(a_i, a_j)$ , represents the overhead for a single address register to consecutively access  $a_i$  then  $a_i$ . E also contains edges that connect the source and sink vertices,  $(a_s, a_i)$  and  $(a_i, a_t), \forall a_i \in S$ . The edges  $(a_s, a_i), \forall a_i \in S$  represent an address register initialization, and have cost  $c_{s,i} = INIT$ . Edges connected to the sink  $a_t$  have cost  $c_{i,t} = 0$ . The final edge  $(a_s, a_t)$  in E connects the source to the sink and represents unused address-registers. It has cost  $c_{s,t}=0$  and infinite capacity. All other edges in E have a capacity of 1. Each unit flow through G represents an assignment of a single address register to a set of variable accesses; thus, a minimum-cost flow through G represents an assignment of address registers to variable accesses with minimal overhead. In other words, the minimum-cost flow through G represents an optimal addressing code for the given access sequence S and memory layout M. An example of a minimum-cost flow graph for the example in Section 1.3 is shown in Figure 3.3. The network flow graph is built using the following access sequence